#### FAMU-FSU College of Engineering Department of Electrical and Computer Engineering

#### PROJECT PROPOSAL AND STATEMENT OF WORK

#### EEL4911C – ECE Senior Design Project I

#### Project Title: Synthetic Active Array Radar Aperture (SAR)

#### <u>Team #</u>: E11

#### Student Team Members:

- Matthew Cammuse, Electrical Engineering (Email: mgc11@my.fsu.edu)

- Joshua Cushion, Electrical Engineering (Email: jlc10e@my.fsu.edu)

- Patrick Delallana, Electrical/Computer Engineering (Email: pnd10@my.fsu.edu)

- Julia Kim, Electrical Engineering (Email: jk09k@my.fsu.edu)

- Malcolm Harmon, Mechanical Engineering (Email: mjh11f@my.fsu.edu)

- **Benjamin Mock**, Industrial Engineering (Email: bam11g@my.fsu.edu)

- Mark Poindexter, Mechanical Engineering (Email: mpp12b@my.fsu.edu)

- Jasmine Vanderhorst, Industrial Engineering (Email:Vanderhorst\_91@yahoo.com)

<u>Senior Design Project Instructor</u>: Dr. Michael Frank <u>Electrical/Computer Engineering Department Advisors</u>: Dr. Simon Foo and Dr. Shonda Bernadin <u>Industrial Engineering Department Advisor</u>: Dr. Okoli <u>Mechanical Engineering Department Advisor</u>: Dr. Collins

> Submitted in partial fulfillment of the requirements for EEL4911C – ECE Senior Design Project I

> > October 20, 2014

#### **Project Executive Summary**

The purpose of the electronic Synthetic Active Aperture Radar (SAR) Imager project, sponsored by Northrop Grumman, is to design and develop a low-cost detection system capable of providing a low, but useful, imagery resolution as a learning experience. In theory, the application of the electronic SAR Imager focuses on security applications and its ability to detect potentially threatening objects such as handguns. This project is sponsored through the FAMU-Foundation with a \$50,000.00 budget with an expected time line of eight months to completion. A radar is an object detection system that uses radio waves to measure characteristics of certain objects and is typically composed of antennas in which transmit pulses of radio waves bounce off the target in the designated range. The wave is reflected off the target and returns a wave to the receiving end of the system which is usually a dish, horn, or some form of waveguide usually located at the same site as the transmission of the wave. In a typical radar, the antenna which usually acts as a transmitter and/or receiver is in a static position. The electronic SAR Imager is a more complicated scenario of radar imaging which allows for the detection of a much greater range by movement of the transmission antenna. This can be seen such applications as aircraft topography; the antenna on the plane would transmit signal to a landscape while the antenna is moving. To create a fixed electronic SAR imager, the design will be constructed with multiple stationary antennas that emit or receive pulses to emulate the theory of an SAR.

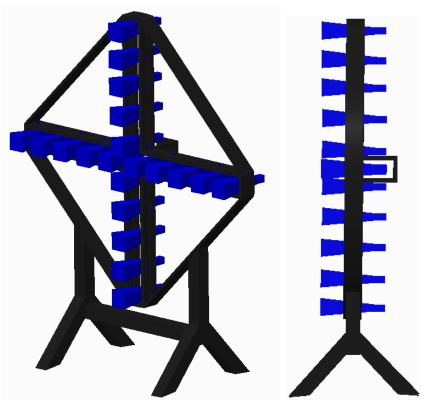

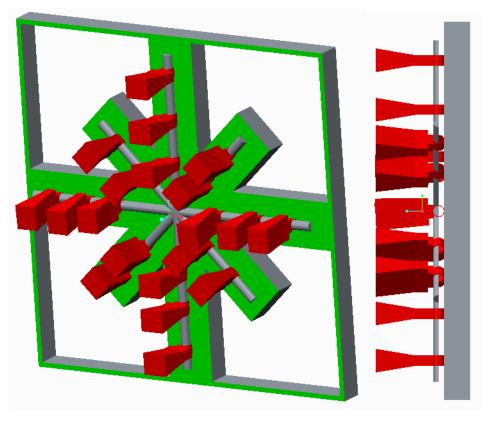

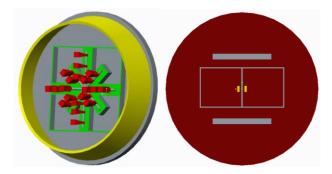

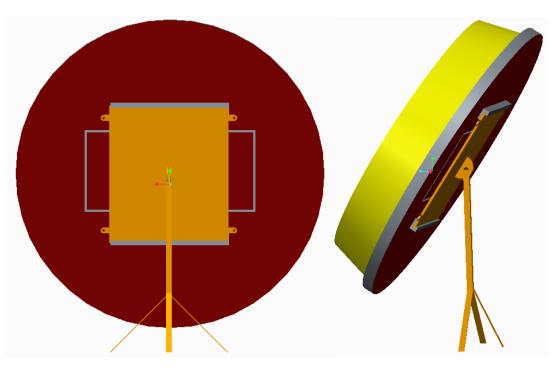

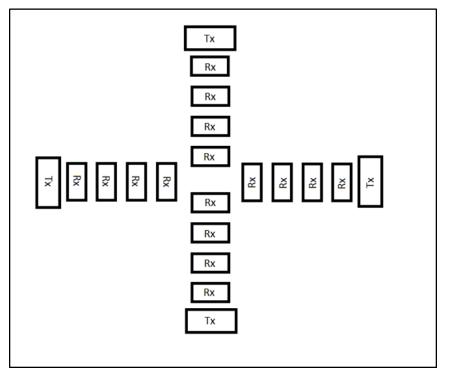

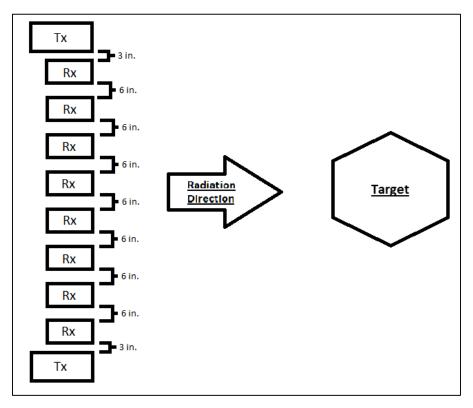

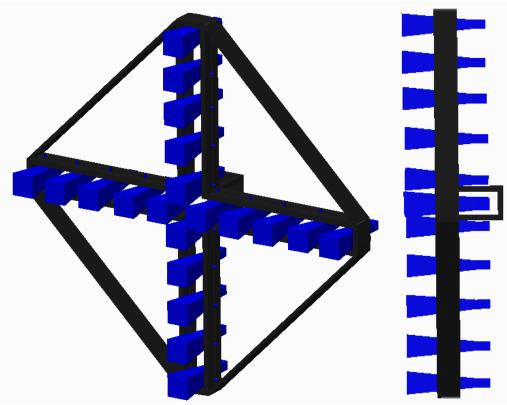

This project will consist of twenty horn antennas: sixteen receive and four transmit. The antenna structure will consist of two linear antenna apertures. Each aperture will contain eight receive antennas placed between two transmit antennas. Two antenna apertures will be utilized and laid across each other creating a T-shaped design with each horn directed towards the target. Besides the center horn antennas, each horn will be angled directionally towards the target. Overall, the design will create four rows of five antennas being placed orthogonal to each other, creating sixteen phase centers per linear antenna aperture and thirty-two phase centers for the whole design. A phase center is the half-way distance between one transmit and one receive antenna in an aperture and represents a receive antenna's center absorbance point or maximum absorbance point. One transmit is responsible for eight phase centers. When placing receive antennas next to each other, additional maximum absorbance points are created. One aperture may only have eight receive antennas but eight additional phase or maximum absorbance points are created. For this project, radar system is required to reach a target twenty feet away and cover a human's body.

The system will be controlled via an FPGA which will sequentially transmit pulse from an antenna and then turn on the receiving antennas/turn off the transmitting antenna pulse to receiving a signal bouncing off the target. This will be done from every orthogonal direction one after the other to give the most data possible. The data would get sampled on a scope and get recorded. If time permits, the FPGA can do more complicated tasks such as storing some of the data that can be output and operated on. This sampled data could then be captured and sent to a PC for image processing. This would most likely be done using software such as Simulink. Overall the goal of this project is to apply engineering design practices and technical knowledge to create a physical schematic of an SAR Imager which would transmit and receive pulse from at least one row of antennas out of the four orthogonal rows.

# Contents

| Project Executive Summary                                          | 2  |

|--------------------------------------------------------------------|----|

| 1 Introduction                                                     | 17 |

| 1.1 Acknowledgements                                               | 17 |

| 1.2 Problem Statement                                              | 17 |

| 1.2.1 General Problem Statement                                    | 17 |

| 1.2.2 General Problem Solution                                     | 17 |

| 1.3 Operating Environment                                          |    |

| 1.4 Intended Use(s) and Intended User(s)                           |    |

| 1.4.1 Intended Use                                                 |    |

| 1.4.2 Intended Users                                               |    |

| 1.5 Assumptions and Limitations                                    |    |

| 1.5.1 Assumptions                                                  |    |

| 1.5.2 Limitations                                                  |    |

| 1.6 Expected End Products and Other Deliverables                   |    |

| 1.6.1 Synthetic Active Aperture Radar Imager                       |    |

| 1.6.2 Documentation and Configuration Flash Drive                  |    |

| 1.6.2.1 Electronic Circuit Schematics                              |    |

| 1.6.2.2 Antenna Structural Schematics                              |    |

| 1.6.2.3 Code and Configuration Files                               |    |

| 2 Concept Generation                                               |    |

| 2.1 Electrical System Design                                       |    |

| 2.1.1 Simple Model                                                 |    |

| 2.1.2 Advanced Model                                               |    |

| 2.2 Horn Antennas                                                  |    |

| 2.2.1 Advanced Receiver: Model No. MA86551                         |    |

| 2.2.1.1 Specifications                                             |    |

| 2.2.1.2 Benefits                                                   |    |

| 2.2.1.3 Drawbacks                                                  |    |

| 2.2.2 Advanced Technical Materials: High Band – Model No. 90-443-6 |    |

| 2.2.2.1 Specifications                                                  |  |

|-------------------------------------------------------------------------|--|

| 2.2.2.2 Benefits                                                        |  |

| 2.2.2.3 Drawbacks                                                       |  |

| 2.2.3 Advanced Technical Materials: High Band – Model No. 75-443-6      |  |

| 2.2.3.1 Specifications                                                  |  |

| 2.2.3.2 Benefits                                                        |  |

| 2.2.3.3 Drawbacks                                                       |  |

| 2.3 Waveguide-to-coaxial Adapters                                       |  |

| 2.3.1 Flann 16094-NF   WR90 to N-Female Waveguide Adapter X-Band        |  |

| 2.3.1.1 Specifications                                                  |  |

| 2.3.1.2 Benefits                                                        |  |

| 2.3.1.3 Drawbacks                                                       |  |

| 2.3.2 Omega Laboratories Model 108 - WR90 to N-Female Waveguide Adapter |  |

| 2.3.2.1 Specifications                                                  |  |

| 2.3.2.2 Benefits                                                        |  |

| 2.3.2.3 Drawbacks                                                       |  |

| 2.3.3 WR90 Waveguide Isolator X-Band 8.2 to 12.4 GHz                    |  |

| 2.3.3.1 Specifications                                                  |  |

| 2.3.3.2 Benefits                                                        |  |

| 2.3.3.3 Drawbacks                                                       |  |

| 2.4 FPGA                                                                |  |

| 2.4.1 Digilent Nexys 2                                                  |  |

| 2.4.1.1 Specifications                                                  |  |

| 2.4.1.2 Benefits                                                        |  |

| 2.4.1.3 Drawbacks                                                       |  |

| 2.4.2 Digilent Nexys 3                                                  |  |

| 2.4.2.1 Specifications                                                  |  |

| 2.4.2.2 Benefits                                                        |  |

| 2.4.2.3 Drawbacks                                                       |  |

| 2.4.3 Digilent Nexys 4 Artix-7                                          |  |

| 2.4.3.1 Specifications                                      |  |

|-------------------------------------------------------------|--|

| 2.4.3.2 Benefits                                            |  |

| 2.4.3.3 Drawbacks                                           |  |

| 2.5 D/A and A/D Pmod Converters                             |  |

| 2.5.1 Digilent PmodDA1 8 bit                                |  |

| 2.5.1.1 Specifications                                      |  |

| 2.5.1.2 Benefits                                            |  |

| 2.5.1.3 Drawbacks                                           |  |

| 2.5.2 Digilent PmodAD1 Two 12-bit                           |  |

| 2.5.2.1 Specifications                                      |  |

| 2.5.2.2 Benefits                                            |  |

| 2.5.2.3 Drawbacks                                           |  |

| 2.6 Voltage Controlled Oscillator (VCO)                     |  |

| 2.6.1 Hittite Microwave Corporation HMC-C028                |  |

| 2.6.1.1 Specifications                                      |  |

| 2.6.1.2 Benefits                                            |  |

| 2.6.1.3 Drawbacks                                           |  |

| 2.6.2 RFMD VCO-520S/STC                                     |  |

| 2.6.2.1 Specifications                                      |  |

| 2.6.2.2 Benefits                                            |  |

| 2.6.2.3 Drawbacks                                           |  |

| 2.7 IQ Demodulator                                          |  |

| 2.7.1 Polyphase Microwave Quadrature Demodulator – AD60100B |  |

| 2.7.1.1 Specifications                                      |  |

| 2.7.2 SigaTek I Q Demodulator – QD27A11                     |  |

| 2.7.2.1 Specifications                                      |  |

| 2.7.2.2 Benefits                                            |  |

| 2.7.2.3 Drawbacks                                           |  |

| 2.8 Switches                                                |  |

| 2.8.1 Single Pole Double Throw (SPDT)                       |  |

| 2.8.1.1 Hittite HMC-C058                                                                                                                                                                                                                                                                                                                                                                   |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.8.1.1.1 Specifications                                                                                                                                                                                                                                                                                                                                                                   |          |

| 2.8.1.1.2 Benefits                                                                                                                                                                                                                                                                                                                                                                         |          |

| 2.8.1.1.3 Drawbacks                                                                                                                                                                                                                                                                                                                                                                        |          |

| 2.8.1.2 UMC SW-L010-2S                                                                                                                                                                                                                                                                                                                                                                     |          |

| 2.8.1.2.1 Specifications                                                                                                                                                                                                                                                                                                                                                                   |          |

| 2.8.1.2.2 Benefits                                                                                                                                                                                                                                                                                                                                                                         |          |

| 2.8.1.2.3 Drawbacks                                                                                                                                                                                                                                                                                                                                                                        |          |

| 2.8.2 Single Pole Four Throw (SP4T)                                                                                                                                                                                                                                                                                                                                                        | 35       |

| 2.8.2.1 Hittite HMC-C071                                                                                                                                                                                                                                                                                                                                                                   |          |

| 2.8.2.1.1 Specifications                                                                                                                                                                                                                                                                                                                                                                   |          |

| 2.8.1.1.2 Benefits                                                                                                                                                                                                                                                                                                                                                                         |          |

| 2.8.1.1.3 Drawbacks                                                                                                                                                                                                                                                                                                                                                                        |          |

| 2.8.2.2 UMC SW-L010-4S                                                                                                                                                                                                                                                                                                                                                                     |          |

| 2.8.2.2.1 Specifications                                                                                                                                                                                                                                                                                                                                                                   |          |

| ~P                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 2.8.2.2.2 Benefits                                                                                                                                                                                                                                                                                                                                                                         |          |

| -                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 2.8.2.2.2 Benefits                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36 |

| 2.8.2.2.2 Benefits                                                                                                                                                                                                                                                                                                                                                                         |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)                                                                                                                                                                                                                                                                                                            |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)<br>2.8.3.1 UMC SW-L010-16S                                                                                                                                                                                                                                                                                 |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)<br>2.8.3.1 UMC SW-L010-16S<br>2.8.3.1.1 Specifications                                                                                                                                                                                                                                                     |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)<br>2.8.3.1 UMC SW-L010-16S<br>2.8.3.1.1 Specifications<br>2.8.3.1.2 Benefits                                                                                                                                                                                                                               |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)<br>2.8.3.1 UMC SW-L010-16S<br>2.8.3.1.1 Specifications<br>2.8.3.1.2 Benefits<br>2.8.3.1.3 Drawbacks                                                                                                                                                                                                        |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)<br>2.8.3.1 UMC SW-L010-16S<br>2.8.3.1.1 Specifications<br>2.8.3.1.2 Benefits<br>2.8.3.1.3 Drawbacks<br>2.8.3.2 AMC MSN-16DR-05                                                                                                                                                                             |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)<br>2.8.3.1 UMC SW-L010-16S<br>2.8.3.1.1 Specifications<br>2.8.3.1.2 Benefits<br>2.8.3.1.3 Drawbacks<br>2.8.3.2 AMC MSN-16DR-05.<br>2.8.3.2.1 Specifications                                                                                                                                                |          |

| 2.8.2.2.2 Benefits.         2.8.2.2.3 Drawbacks.         2.8.3 Single Pole 16 Throw (SP16T).         2.8.3.1 UMC SW-L010-16S         2.8.3.1.1 Specifications         2.8.3.1.2 Benefits.         2.8.3.1.3 Drawbacks         2.8.3.2 AMC MSN-16DR-05.         2.8.3.2.1 Specifications         2.8.3.2.2 Benefits.                                                                        |          |

| 2.8.2.2.2 Benefits.         2.8.2.2.3 Drawbacks         2.8.3 Single Pole 16 Throw (SP16T).         2.8.3 Single Pole 16 Throw (SP16T).         2.8.3.1 UMC SW-L010-16S         2.8.3.1.1 Specifications         2.8.3.1.2 Benefits.         2.8.3.1.3 Drawbacks         2.8.3.2 AMC MSN-16DR-05.         2.8.3.2.1 Specifications         2.8.3.2.2 Benefits.         2.8.3.2.3 Drawbacks |          |

| 2.8.2.2.2 Benefits<br>2.8.2.2.3 Drawbacks<br>2.8.3 Single Pole 16 Throw (SP16T)<br>2.8.3.1 UMC SW-L010-16S<br>2.8.3.1.1 Specifications<br>2.8.3.1.2 Benefits<br>2.8.3.1.3 Drawbacks<br>2.8.3.2 AMC MSN-16DR-05<br>2.8.3.2.1 Specifications<br>2.8.3.2.2 Benefits<br>2.8.3.2.2 Benefits<br>2.8.3.2.3 Drawbacks<br>2.9 VHDL Software Generators                                              |          |

| 2.9.2 National Instruments: <i>LabVIEW</i>                          |

|---------------------------------------------------------------------|

| 2.9.2.1 Benefits                                                    |

| 2.9.2.2 Drawbacks                                                   |

| 2.9.3 Software Selection                                            |

| 2.10 Structure                                                      |

| 2.10.1 Design 1                                                     |

| 2.10.1.1 3-D Model                                                  |

| 2.10.1.2 Benefits                                                   |

| 2.10.1.3 Drawbacks                                                  |

| 2.10.2 Design 2                                                     |

| 2.10.2.1 3-D Model: Horn Structure                                  |

| 2.10.2.2 Benefits of Horn Structure                                 |

| 2.10.2.2.1 Material Benefits                                        |

| 2.10.2.3 Drawbacks of Horn Structure                                |

| 2.10.2.3.1 Material Drawbacks                                       |

| 2.10.2.4 3-D Model: Cover for Horn Structure                        |

| 2.10.2.5 Benefits of Cover for Horn Structure                       |

| 2.10.2.5.1 Material Benefits                                        |

| 2.10.2.6 Drawbacks of Cover for Horn Structure                      |

| 2.10.2.6.1 Material Drawbacks                                       |

| 2.10.2.7 3-D Model: Tripod Stand for Horn Structure and Cover       |

| 2.10.2.8 Benefits of Tripod Stand                                   |

| 2.10.2.9 Drawbacks of Tripod Stand                                  |

| 2.11 Alignment Laser                                                |

| 2.11.1 Monster Military G768BC Adjustable Focus Green Laser Pointer |

| 2.11.1.1 Benefits                                                   |

| 2.11.1.2 Drawbacks                                                  |

| 2.11.2 Focusable Green Line Generator Module                        |

| 2.11.2.1 Benefits                                                   |

| 2.11.2.2 Drawbacks                                                  |

| 2.11.3 Quarton Laser Module VLM-532-47 LPT           |    |

|------------------------------------------------------|----|

| 2.11.3.1 Benefits                                    |    |

| 2.11.3.2 Drawbacks                                   |    |

| 3 Proposed Design                                    |    |

| 3.1 Design Overview                                  |    |

| 3.1.1 Electrical System                              |    |

| 3.1.1.1 FPGA                                         |    |

| 3.1.1.1.1 FPGA Demo Board Major Components           | 47 |

| 3.1.1.1.1 Physical Schematic of Circuit              |    |

| 3.1.1.2 Transmit Signal Path                         | 49 |

| 3.1.1.2.1 Transmit Signal Path Design Components     | 49 |

| 3.1.1.3 Receive Signal Path                          | 50 |

| 3.1.1.3.1 Receive Signal Path Design Components      | 50 |

| 3.1.1.4 Power Distribution Design                    | 50 |

| 3.1.2 Antenna Design                                 | 50 |

| 3.1.3 Structure                                      |    |

| 3.1.3.1 3-D Model of T-Shape Horn Structure          | 52 |

| 4 Statement of Work (SOW)                            |    |

| 4.1 Task 1: Project Management                       |    |

| 4.1.1 Objectives                                     | 55 |

| 4.1.2 Approach                                       | 55 |

| 4.2 Task 2: Treasurer                                | 55 |

| 4.2.1 Objective                                      | 55 |

| 4.2.2 Approach                                       | 56 |

| 4.2.2.1 Subtask 2.1: Budget Implementation & Control | 56 |

| 4.2.2.1.1 Objective                                  | 56 |

| 4.2.2.1.2 Approach                                   | 56 |

| 4.2.2.1.3 Verification                               | 56 |

| 4.3 Task 3: Product Procurement                      | 56 |

| 4.3.1 Objective                                      |    |

| 4.3.2 Approach                                               | 56 |

|--------------------------------------------------------------|----|

| 4.3.2.1 Verification                                         | 56 |

| 4.3.2.2 Subtask 3.1: Vendor Inquiry                          | 57 |

| 4.3.2.2.1 Objective                                          | 57 |

| 4.3.2.2.2 Approach                                           | 57 |

| 4.3.2.2.3 Verification                                       | 57 |

| 4.3.2.3 Subtask 3.2: Product Purchasing                      | 57 |

| 4.3.2.3.1 Objective                                          | 57 |

| 4.3.2.3.2 Approach                                           | 57 |

| 4.3.2.3.3 Verification                                       | 57 |

| 4.4 Task 4: Facility Procurement                             | 58 |

| 4.4.1 Objective                                              | 58 |

| 4.4.2 Approach                                               | 58 |

| 4.4.3 Verification                                           | 58 |

| 4.4.3.1 Subtask 4.1: Weekly Team Meeting Room Procurement    | 58 |

| 4.4.3.1.1 Objective                                          | 58 |

| 4.4.3.1.2 Approach                                           | 58 |

| 4.4.3.2 Subtask 4.2: Weekly Sponsor Meeting Room Procurement | 58 |

| 4.4.3.2.1 Objective                                          | 58 |

| 4.4.3.2.2 Approach                                           | 58 |

| 4.4.3.2.3 Verification                                       | 59 |

| 4.4.3.3 Subtask 4.3: Facility Procurement                    | 59 |

| 4.4.3.3.1 Objective                                          | 59 |

| 4.4.3.3.2 Approach                                           | 59 |

| 4.4.3.3.3 Verification                                       | 59 |

| 4.5 Task 5: Industrial Engineering                           | 59 |

| 4.5.1 Objective                                              | 59 |

| 4.5.2 Approach                                               | 59 |

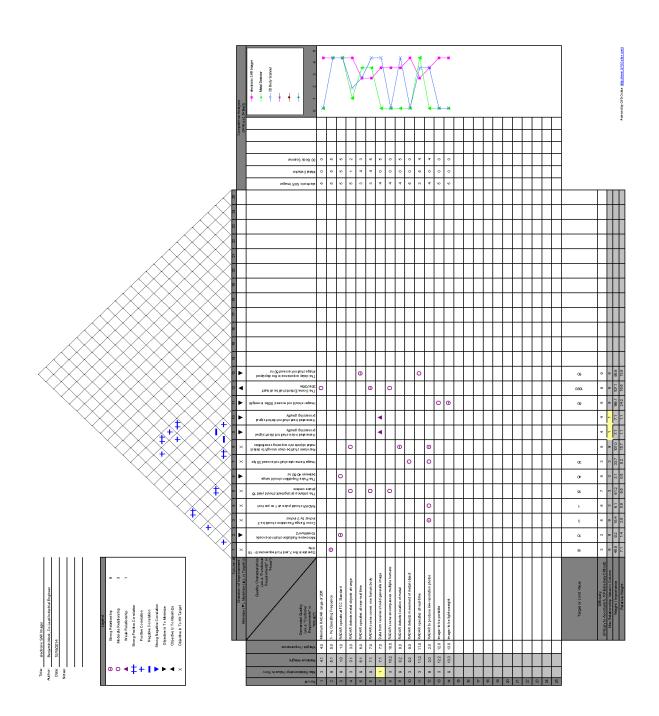

| 4.5.2.1 Subtask 5.1: House of Quality                        | 60 |

| 4.5.2.1.1 Objective                                          | 60 |

| 4.5.2.1.2 Approach                              | 60 |

|-------------------------------------------------|----|

| 4.5.2.2 Subtask 5.2: Voice of The Customer Tree | 60 |

| 4.5.2.2.1 Objective                             | 60 |

| 4.5.2.2.2 Approach                              | 60 |

| 4.6 Task 6: Risk Management                     | 60 |

| 4.6.1 Objective                                 | 60 |

| 4.6.2 Approach                                  | 60 |

| 4.6.2.1 Subtask 6.1: Initial Risk Assessment    | 61 |

| 4.6.2.1.1 Objective                             | 61 |

| 4.6.2.1.2 Approach                              | 61 |

| 4.6.2.2 Subtask 6.2 Continual Risk Assessment   | 61 |

| 4.6.2.2.1 Objective                             | 61 |

| 4.6.2.2.2 Approach                              | 61 |

| 4.7 Task 7: Antenna Design                      | 61 |

| 4.7.1 Objective                                 | 61 |

| 4.7.2 Approach                                  | 61 |

| 4.7.2.2 Subtask 7.2: Structural Design          |    |

| 4.7.2.2.1 Objective                             |    |

| 4.7.2.2.2 Approach                              |    |

| 4.7.2.3 Subtask: Structure                      |    |

| 4.7.2.3.1 Objective                             |    |

| 4.7.2.2.3.2 Approach                            | 62 |

| 4.7.2.4 Subtask: Frame                          |    |

| 4.7.2.4.1 Objective                             | 62 |

| 4.7.2.4.2 Approach                              |    |

| 4.7.2.5 Subtask: Horn Alignment                 | 63 |

| 4.7.2.5.1 Objective                             | 63 |

| 4.7.2.5.2 Approach                              | 63 |

| 4.8 Task 8: Electrical Design                   | 63 |

|                                                 | 63 |

| 4.8.2 Approach                                                       | 63 |

|----------------------------------------------------------------------|----|

| 4.8.2.1 Subtask 8.1: Simulations                                     | 63 |

| 4.8.2.1.1 Objective                                                  | 63 |

| 4.8.2.1.2 Approach                                                   | 63 |

| 4.8.2.2 Subtask 8.2: Determining Radar Range Equation Parameters     | 63 |

| 4.8.2.2.1 Objective                                                  | 63 |

| 4.8.2.2.2 Approach                                                   | 63 |

| 4.8.2.3 Subtask 8.3: Component Selection and Analysis                | 64 |

| 4.8.2.3.1 Objective                                                  | 64 |

| 4.8.2.3.2 Approach                                                   | 64 |

| 4.9 Task 9: Field Programmable Gate Array Control Processing         | 64 |

| 4.9.1 Objective                                                      | 64 |

| 4.9.2 Approach                                                       | 64 |

| 4.9.2.1 Subtask 9.1: Code for Pulse Generation                       | 64 |

| 4.9.2.1.1 Objective                                                  | 64 |

| 4.9.2.1.2 Approach                                                   | 64 |

| 4.9.2.2 Subtask 9.2: Timing                                          | 65 |

| 4.9.2.2.1 Objective                                                  | 65 |

| 4.9.2.2.2 Approach                                                   | 65 |

| 4.9.2.3 Subtask 9.3: Information Storage in Memory                   | 65 |

| 4.9.2.3.1 Objective                                                  | 65 |

| 4.9.2.3.2 Approach                                                   | 65 |

| 4.9.2.4 Subtask 9.4: Output to Display                               | 65 |

| 4.9.2.4.1 Objective                                                  | 65 |

| 4.9.2.4.2 Approach                                                   | 65 |

| 4.10 Task 10: System Assembly                                        | 65 |

| 4.10.1 Objective                                                     | 65 |

| 4.10.2 Approach                                                      | 65 |

| 4.10.2.1 Subtask 10.1: Mechanical Assembly of Antennas and Equipment | 66 |

| 4.10.2.1.1 Objective                                                 | 66 |

| 4.10.2.1.2 Approach                                      | 66 |

|----------------------------------------------------------|----|

| 4.10.2.2 Subtask 11.2: Electrical Assembly of Components | 66 |

| 4.10.2.2.1 Objective                                     | 66 |

| 4.10.2.2.2 Approach                                      | 66 |

| 4.11 Task 11: System Testing Plan                        | 66 |

| 4.11.1 Objective                                         | 66 |

| 4.11.2 Approach                                          | 66 |

| 4.11.2.1 Subtask 12.1: Transmit Pulse                    | 66 |

| 4.11.2.1.1 Objective                                     | 66 |

| 4.11.2.1.2 Approach                                      | 66 |

| 4.11.2.2 Subtask 12.2: Receive Pulse                     | 66 |

| 4.11.2.2.1 Objective                                     | 66 |

| 4.11.2.2.2 Approach                                      | 66 |

| 4.12 Task 12: Result Evaluation                          | 67 |

| 4.12.1 Objective                                         | 67 |

| 4.12.2 Approach                                          | 67 |

| 4.12.3 Outcomes of Task                                  | 67 |

| 4.13 Task 13: Project Documentation                      | 67 |

| 4.13.1 Objective                                         | 67 |

| 4.13.2 Approach                                          | 67 |

| 4.13.2.1 Subtask 13.1: Weekly Meeting Minutes            | 67 |

| 4.13.2.1.1 Objective                                     | 67 |

| 4.13.2.1.2 Approach                                      | 68 |

| 4.13.2.1.3 Outcomes of Task                              | 68 |

| 4.13.2.2 Subtask 13.2: Project Reports and Presentations | 68 |

| 4.13.2.2.1 Objective                                     | 68 |

| 4.13.2.2.2 Approach                                      | 68 |

| 4.13.2.2.3 Outcomes of Task                              | 68 |

| 4.13.2.3 Subtask 14.3: Testing Reports                   | 68 |

| 4.13.2.3.1 Objective                                     | 68 |

| 4.13.2.3.2 Approach                     | 68 |

|-----------------------------------------|----|

| 4.13.2.3.3 Outcomes of Task             | 69 |

| 5 Risk Assessment                       | 69 |

| 5.1 Component Procurement Risks         | 69 |

| 5.1.1 Faulty Lead Time Estimate         | 69 |

| 5.1.1.1 Assessment                      | 69 |

| 5.1.1.2 Mitigation Strategy             | 69 |

| 5.1.2 Procurement Policy Difficulties   | 69 |

| 5.1.2.1 Assessment                      | 69 |

| 5.1.2.2 Mitigation Strategy             | 69 |

| 5.1.3 Faulty Components                 | 69 |

| 5.1.3.1 Assessment                      | 69 |

| 5.1.3.2 Mitigation Strategy             | 70 |

| 5.1.4 Necessary Background Research     | 70 |

| 5.1.4.1 Assessment                      | 70 |

| 5.1.4.2 Mitigation Strategy             | 70 |

| 5.1.5 Unanticipated Tool Procurement    | 70 |

| 5.1.5.1 Assessment                      | 70 |

| 5.1.5.2 Mitigation Strategy             | 70 |

| 5.1.6 Fragile Components                | 70 |

| 5.1.6.1 Assessment                      | 70 |

| 5.1.6.2 Mitigation Strategy             | 70 |

| 5.1.7 Non-Integrated Circuit Components | 71 |

| 5.1.7.1 Assessment                      | 71 |

| 5.1.7.2 Mitigation Strategy             | 71 |

| 5.1.8 Component Failure                 | 71 |

| 5.1.8.1 Assessment                      | 71 |

| 5.1.8.2 Mitigation Strategy             | 71 |

| 5.2 Facility Procurement Risks          | 71 |

| 5.2.1 Proper Storage                    | 71 |

| 5.2.1.1 Assessment                                   | 71 |

|------------------------------------------------------|----|

| 5.2.1.2 Mitigation Strategy                          |    |

| 5.2.2 Component Tolerance to Electrostatic Discharge |    |

| 5.2.2.1 Assessment                                   |    |

| 5.2.2.2 Mitigation Strategy                          |    |

| 5.2.3 Facility Availability                          |    |

| 5.2.3.1 Assessment                                   |    |

| 5.2.3.2 Mitigation Strategy                          |    |

| 5.2.4 Testing Safety                                 |    |

| 5.2.4.1 Assessment                                   |    |

| 5.2.4.2 Mitigation Strategy                          |    |

| 5.3 Design & Control Risks                           |    |

| 5.3.1 Inaccurate Team Scheduling                     |    |

| 5.3.1.1 Assessment                                   |    |

| 5.3.1.2 Mitigation Strategy                          |    |

| 5.3.2 Presence of Noise                              |    |

| 5.3.2.1 Assessment                                   |    |

| 5.3.2.2 Mitigation Strategy                          |    |

| 5.3.3 Heat Generated                                 |    |

| 5.3.3.1 Assessment                                   |    |

| 5.3.3.2 Mitigation Strategy                          |    |

| 5.3.4 Component Vibration                            |    |

| 5.3.4.1 Assessment                                   |    |

| 5.3.4.2 Mitigation Strategy                          |    |

| 5.3.5 Limited Idle Time on Gantt chart               |    |

| 5.3.5.1 Assessment                                   |    |

| 5.3.5.2 Mitigation Strategy                          |    |

| 5.3.6 Horn Structure, Attachment, & Mounting         |    |

| 5.3.6.1 Assessment                                   |    |

| 5.3.6.2 Mitigation Strategy                          |    |

| 5.3                                                   | .7 Part Machining                                 | 75 |

|-------------------------------------------------------|---------------------------------------------------|----|

| 5                                                     | 5.3.7.1 Assessment                                | 75 |

| 5                                                     | 5.3.7.2 Mitigation Strategy                       | 75 |

| 5.3                                                   | .8 Team Member Scheduling Conflicts               | 75 |

| 5                                                     | 5.3.8.1 Assessment                                | 75 |

| 5                                                     | 5.3.8.2 Mitigation Strategy                       | 75 |

| 5.3                                                   | .9 Missed Project Deadlines                       | 75 |

| 5                                                     | 5.3.9.1 Assessments                               | 75 |

| 5                                                     | 5.3.9.2 Mitigation Strategies                     | 75 |

| 5.3                                                   | .10 Software Development Risks                    | 76 |

| 5                                                     | 5.3.10.1 Assessment                               | 76 |

| 5                                                     | 5.3.10.2 Mitigation Strategy                      | 76 |

| 6 Qualifications and Responsibilities of Project Team |                                                   |    |

| 6.1 T                                                 | eam Qualifications                                | 76 |

| 6.1                                                   | .1 Jasmine Vanderhorst                            | 76 |

| 6.1                                                   | .2 Matthew Cammuse                                | 76 |

| 6.1                                                   | .3 Malcolm Harmon                                 | 77 |

| 6.1                                                   | .4 Patrick Delallana                              | 77 |

| 6.1                                                   | .5 Benjamin Mock                                  | 77 |

| 6.1                                                   | .6 Joshua Cushion                                 | 78 |

| 6.1                                                   | .7 Julia Kim                                      | 78 |

| 6.1                                                   | .8 Mark Poindexter                                | 78 |

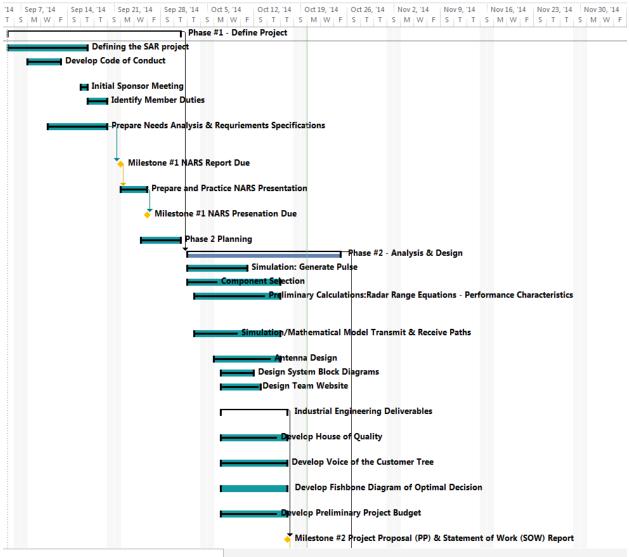

| 7 Sched                                               | lule                                              | 79 |

| 8 Budge                                               | et Estimate                                       | 81 |

| 9 Delive                                              | erables                                           | 82 |

| 9.1 H                                                 | lardware                                          | 83 |

| 9.2 S                                                 | oftware                                           | 83 |

| 9.3 R                                                 | eports                                            | 83 |

| 9.3                                                   | .1 Needs Analysis and Specifications Requirements | 83 |

| 9.3                                                   | .2 Project Proposal and Statement of Work         | 83 |

| 9.3.3 System-Level Design Review |    |

|----------------------------------|----|

| 9.3.4 Detailed Design Review     | 83 |

| 9.3.5 Final Presentation         |    |

| 9.3.6 Team Website               | 84 |

| Appendix                         | 87 |

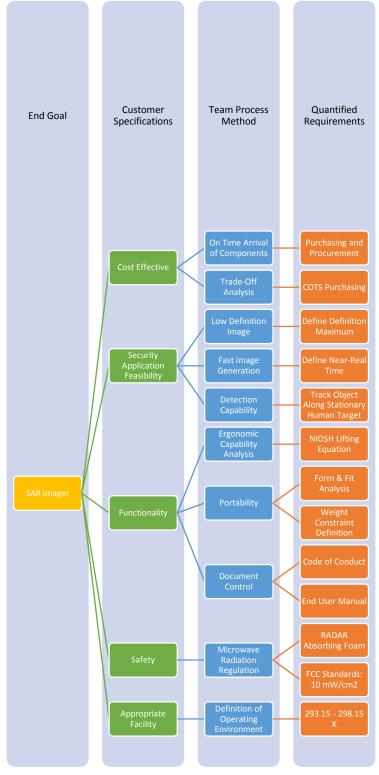

| A1 Voice of the Customer Tree    | 87 |

| A2 Team Resumes                  | 88 |

| A3 House of Quality              |    |

| A4 Gantt Chart                   |    |

# 1 Introduction

#### 1.1 Acknowledgements

The electronic Synthetic Active Aperture Radar (SAR) Imager team would like to extend thanks to the stakeholders of this project from Northrop Grumman and the FAMU-FSU College of Engineering sponsors. First and foremost to the corporate sponsors at Northrop Grumman, we are most grateful for the generous \$50,000 financial contribution to the FAMU Foundation to support research, equipment procurement, and work efforts on the project. In addition to financial contributions, the team also thanks Northrop Grumman for resource support from Peter Stenger, who continually provided technical support, guidance, and direction throughout the duration of the project. We would like to thank Dr. Michael Frank, Dr. Simon Foo, Dr. Shonda Bernadin, Dr. Bruce Harvey, and Dr. Rajendra Arora from the Electrical & Computer Engineering Department for their continued efforts to advise the team in making practical engineering design decisions. Also, we would like to thank Dr. Nikhil Gupta, Dr. Scott Helzer, Dr. Emmanuel Collins, Ricardo Aleman, and Samuel Botero from the Mechanical Engineering department for their contributions in developing professionalism, providing continuous feedback for improvement, and supporting the mechanical design of the SAR Imager system. Finally, we thank Dr. Okenwa Okoli, Dr. James Dobbs, Emily Hammel, and Margaret Scheiner from the Industrial Engineering department for their help in project management, scheduling, and quality engineering.

## **1.2 Problem Statement**

#### 1.2.1 General Problem Statement

The number one priority of this project is to create a physical schematic of a radar system with synthetic-aperture radar theory using COTS (commercial off the shelf) components. The theory behind an SAR Imager requires a mobile transmission and receiving antenna to capture a greater range and/or clearer image of what is being targeted. Since a mobile antenna would require a device which moves the antenna and the team does not have the capability or timeframe to make such a device, we will supplement the framework of a single moveable antenna with a system having multiple antennas to emit and receive signal from different locations. The theory behind emitting and receiving signals on a single target from multiple locations will still be implanted, but instead of using one moving antenna the team will use multiple stationary antennas that emit and receive signals from different locations.

#### 1.2.2 General Problem Solution

The solution will be tackled in several steps. There are three disciplines to this project: Electrical/Computer Engineering, Mechanical Engineering, and Industrial Engineering.

The Electrical/Computer Engineers will design a stationary schematic of a radar system which has twenty antennas overall with sixteen being receive antennas and four being transmit antennas. These antennas will be separated into four rows of five antennas each. Each of these

four rows will be placed orthogonal to each other, and there will be an epicenter between these four rows which is where the target will be. The rows of five will be separated by twenty feet in each direction from the target, and the system that controls the emitting and receiving of signal from the antennas will be controlled via an FPGA. It is the job of the Electrical/Computer engineers to design a workable schematic of the system that receive and emit signals from at least one row of antennas. This also includes the programming of the FPGA board, signal processing, and possibly even image processing of data if the project goes further than expected. The Electrical/Computer Engineers will be the ones to determine almost all of the theory and components of the system, thus making them the base of the project.

The Mechanical Engineers will design the physical structure of the antennas and the associated horns that go with them. The Mechanical engineers will work very closely with the Electrical engineer who specializes in antennas to design the proper horn shape and the spacing between each of the antennas. The Mechanical Engineers also have a role in helping the Electrical Engineers set up all of the components and equipment of the system and making sure that they are working properly as well. It is vitally important for the Mechanical and Electrical Engineers to work in close contact since the Mechanical portion of this project deals with the physical design of the antennas which transmit and emit signal.

The Industrial Engineers have a primary role in managing the human factors, risk analysis, the project schedule, and the overall budget of the system. The Industrial Engineers will also be in charge of helping the Electrical Engineers acquire and order the specific components needed for the system. Industrial Engineers will also be in close contact with the school and the sponsor since they will be the ones who actually go and submit the orders for purchase. Industrial Engineers will also be of utmost importance when making administrative decisions within the team due to their knowledge of cost engineering and optimization.

#### **1.3 Operating Environment**

The operating environment will be those locations of primary concern for homeland security applications such as airports, public schools, museums, etc. These locations will demand that the SAR Imager properly functions at average room temperature (293.15 - 298.15 K) and within average humidity (30 - 50%) [1]. The SAR Imager should be able to operate in the presence of other electronics and RADARs and not be influenced by them in their main operation: determining the hidden threat of hidden weaponry. This system should be able to operate at a nonstop pace when needed and also be equipped with adjustments to be set-up in the specified location on interest.

#### 1.4 Intended Use(s) and Intended User(s)

#### 1.4.1 Intended Use

The intended use for the SAR Imager will be for theoretical implementation and testing. Tests to check for the transmission and receiving of pulse by the antennas of this project will be the primary use for the system. A mannequin will act as the target to abide by FSU campus medical standards. If time allows, more complicated aspects such as image processing can be used to generate an image.

#### 1.4.2 Intended Users

The intended users for the SAR Imager will primarily be the student members of the team. Any advisors or the sponsor may want to test out the system for themselves to check progress and that is a viable option as well. As a research project, this project only intends for an operating physical schematic of the project, not a fully functional prototype. The end result should have a physical system that transmits and receives signal that is controlled/timed via an FPGA.

# 1.5 Assumptions and Limitations

## 1.5.1 Assumptions

This project is based upon the following assumptions:

- The radar should operate at frequencies safe for human interaction.

- The radar must be capable of detecting metal and/or threatening objects on a person's body from a distance.

- The radar must be operating at near real-time.

- The data from the receiver should generate polynomial images on a display screen. Then based on color identification, it should be easy to pin point an object's location. A selected color would represent a received signal, and if that color appears on the screen, an object has been located.

- The field programmable gate array (FPGA) board must have a clock of 100 MHz.

- The FPGA board should have Peripheral Module (Pmod) connectors to add analog-to-digital (A/D) and digital-to-analog (D/A) converters.

# 1.5.2 Limitations

The decisions in this project are confined by the following limitations:

- The distance to the scene to be imaged must be 20 feet. (REQF-002)

- The area to be imaged, also known as scene extent, must cover the width of a person and should ideally cover the person's torso and legs. However, the scene extent will be based on the type of horn antennas selected. (REQF-003)

- The frequency range should be within the X- or Ku- band operating frequency, which is a range of 8 to 12 GHz for X-band and 12 to 18 GHz for Ku-band. (REQF-001)

- The cross range and down range resolution are determined based on the employed beamwidth and distance between the antennas and target. (REQF-004)

- The down range resolution must be low so it does not take a thorough image of the body, but has enough depth. (REQF-005)

- The pulse width should be at about 20 nanoseconds so the pulse can travel to and from the scene. (REQF-006)

- The number of phase centers for the system is sixteen. (REQF-010)

- The number of antennas to be used for the system is sixteen receive antennas and four transmit antennas. (CONS-001)

- Antennas must be placed close together at equal distances apart and be precisely pointed at target. (CONS-002)

- To use the system for testing, the room must be bigger than 20 feet x 15 feet.

# 1.6 Expected End Products and Other Deliverables

## 1.6.1 Synthetic Active Aperture Radar Imager

The SAR Imager system will be designed and physically implemented by April 2015. The sponsor in particular does not have a deadline, but the College of Engineering's deadline for completion of projects is April 2015. The end product of this project will be a testable conceptual design of an electronic SAR Imager. The electronic SAR Imager will have the ability to receive and transmit pulses on at least one row of antennas out of the four orthogonal rows on the whole schematic. A summary of the radar system's components are listed below:

- 1 Field Programmable Gate Array (FPGA) board

- 1 Power Supply

- 4 Transmit Antennas

- 16 Receive Antennas

- 1 Voltage Controlled Oscillator (VCO)

- 1 IQ Demodulator

- 4 Single Pole Double Throw (SPDT) Switch

- 4 Multipliers

- 5 Variable Attenuators

- 4 Power Amplifiers

- 4 Isolators

- 1 Low Noise Amplifier (LNA)

- 1 Dual Active Low Pass Filter (LPF)

- 1 Dual Level Shift

- 1 VGA Display

- 2 Analog-to-Digital Converters

- 1 Digital-to-Analog Converter

#### 1.6.2 Documentation and Configuration Flash Drive

## 1.6.2.1 Electronic Circuit Schematics

The electronic circuit model developed will be saved in different formats to the Documentation and Configuration flash drive. This will be completed by April 2015.

#### 1.6.2.2 Antenna Structural Schematics

The structural design of the antennas and the supporting system will be be saved to the Documentation and Configuration flash drive. This will be completed by April 2015.

## 1.6.2.3 Code and Configuration Files

The VHDL code and configuration files developed for the electronic SAR imager will be organized in a .zip file and saved into the Documentation and Configuration flash drive. This will be completed by April 2015.

# 2 Concept Generation

# 2.1 Electrical System Design

The electrical system is at the center of the SAR Imager and interacts with each of the subsystems. It is needed to generate the radio frequency (RF) signals, receive the reflected RF signals, process the data, and generate and output imagery. The team evaluated two different models suggested by the sponsor: (1) a simple model that uses test equipment and processes the imagery using a separate program after all of the data has been collected, and (2) an advanced model that processes the imagery as the data is collected.

#### 2.1.1 Simple Model

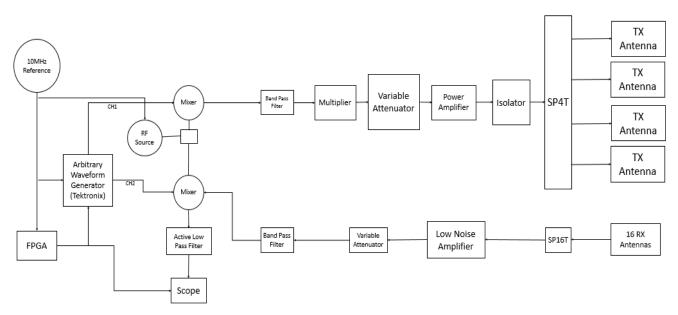

The Simple Model design shown in Figure 1 is the basic option for an electrical system for the SAR Imager that uses test equipment to handle the major functions, such as generating the pulses and collecting and processing the received data. In this design a function generator is used to output the pulse waveforms that feed into the radio frequency source. On the receiving end, the data is captured and collected by the oscilloscope which will allow for the post-processing of the imagery to be completed using software on a computer. The FPGA in this design is necessary only to provide a stable trigger to control the switches. An advantage to this system is that it does not rely on the FPGA to complete the image processing; therefore, less programming firmware is required for the FPGA. A disadvantage to this design is that it does not allow for imagery data to be processed as it is collected, thus, any necessary adjustments to the hardware cannot be made until the end of the data collection period.

Figure 1: Simple Model using Test Equipment

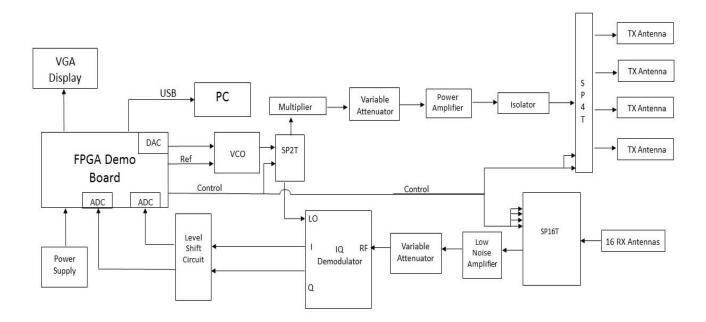

#### 2.1.2 Advanced Model

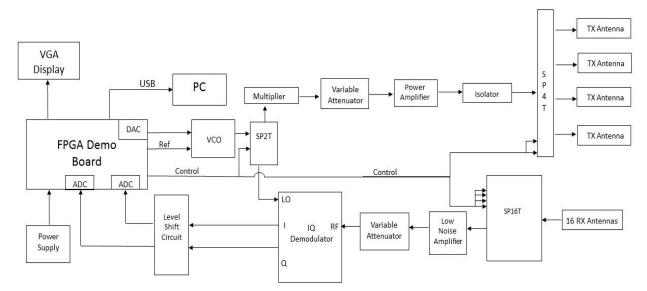

The Advanced Design shown in Figure 2 does not include any test equipment and relies heavily on the FPGA. The FPGA is responsible for the signal processing, generation of the pulse waveforms that input into the RF sources, and switching circuitry, as well as outputting the imagery to a display. An advantage to this design is that it does not require test equipment to process the imagery which means any necessary adjustments to the system can be made while the tests are being conducted. A disadvantage to this design is that it requires more processing in the FPGA which creates the task of writing firmware to handle the signal processing.

Figure 2: Advanced Model Block Diagram

# 2.2 Horn Antennas

The twenty horn antennas will provide high efficiency in directional propagation. With the linear alignment of multiple horn antennas, side lobes can be combined, thus creating twice the amount of phase centers. Selecting the necessary horns requires consideration into price, range of frequencies, gain level, and beamwidth in both the electromagnetic and magnetic plane. Primarily, each horn is required to radiate within X-band frequencies: 8 - 12.4 GHz. The best option from the list below is the Advanced Receiver: Model No. MA86551. It radiates the necessary frequencies and is significantly less in price compared to the other two options. However, its gain level is also significantly reduced which does create a larger scene extent.

- Requirements:

- Quantity: 20

- X-Band Frequency Range: 8 12.4 GHz

# 2.2.1 Advanced Receiver: Model No. MA86551

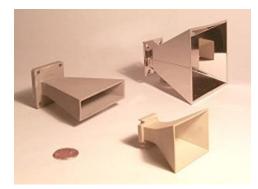

The Advanced Receiver horn antenna is a highly affordable X-band horn antenna that will expand the scene extent and provide complex and vivid results. These horn antennas are the preferred option due to their low-cost. The Model No. MA86551 horn antenna is located at the top right corner of Figure 3.

#### 2.2.1.1 Specifications

- Frequency Range: 8-12.4 GHz

- Gain: 17 dBi

- H-Plane (Azimuth) beamwidth: 25°

- E-Plane (Altitude) beamwidth: 25°

- RF Connection: Mates with UG-39/U

- Height: 3 in.

- Width: 3.7 in

- Length: 3 in.

- Weight: N/A

- Price per horn: \$20.00

Figure 3: Advanced Receiver: X-Band horn antenna

## 2.2.1.2 Benefits

- Extremely cheap. The Advanced receiver horn antennas are at an abnormally low starting price for typical horn antenna.

- The RF connection is also easy to come by and relatively cheap.

- Small: The antennas will be easy to assemble onto a structure and do not require a lot of storage space.

## 2.2.1.3 Drawbacks

• Low gain means the horn antennas beamwidth is much larger, which opposes the initial purpose of scanning a scene extent that is only thirty inches wide.

# 2.2.2 Advanced Technical Materials: High Band – Model No. 90-443-6

Figure 4 is a visual aid to the high band horn antennas which could be used for the radar system.

# 2.2.2.1 Specifications

- Frequency Range: 8.20-12.4 GHz

- Gain: 24 dBi

- H-Plane (Azimuth) beamwidth: 10.6°

- E-Plane (Altitude) beamwidth: 8.8°

- RF Connection: WR90

- Height: 7 in.

- Width: 10 in.

- Length: 20.2 in

- Weight: 3.13 lbs

- Price per horn: \$465.50

Figure 4: ATM High Band Horn Antennas

#### 2.2.2.2 Benefits

- High Gain value: smaller scene extent and narrower beamwidths

- Necessary X-band frequencies

# 2.2.2.3 Drawbacks

- Expensive: Buying twenty horns would hurt the budget.

- Size: These are the largest horns out of the three options. Being almost two feet long would cause the design for the holding structure to be larger and more expensive. In addition, finding the necessary storage space for these antennas would be difficult.

# 2.2.3 Advanced Technical Materials: High Band – Model No. 75-443-6

Figure 4 is a visual aid to the high band horn antennas which could be used for the radar system.

## 2.2.3.1 Specifications

- Frequency Range: 10-15 GHz

- Gain: 24 dBi

- H-Plane (Azimuth) beamwidth: 10.5°

- E-Plane (Altitude) beamwidth: 8.9°

- RF Connection: WR75

- Height: 5.73 in.

- Width: 8.07 in.

- Length: 17 in.

- Weight: N/A

- Price per horn: \$522.50

#### 2.2.3.2 Benefits

• High Gain value: smaller scene extent and narrower beamwidths

## 2.2.3.3 Drawbacks

- Large in size: Finding the necessary storage space will be difficult

- Slight higher frequency range: Range reaches into the Ku-band frequencies and does not cover the entire X-band frequency range.

- Expensive: buying twenty horns would hurt the budget

# 2.3 Waveguide-to-coaxial Adapters

A waveguide adapter will be connected to each antenna and converts coax connection to waveguide. Waveguide adapters will be installed directly onto each waveguide horn antenna or onto the waveguide run extension.

- Requirements:

- Frequency Range: 8-12 GHz

- o Quantity: 20

## 2.3.1 Flann 16094-NF | WR90 to N-Female Waveguide Adapter X-Band

Figure 5 is a picture of one of the options for a waveguide-to-coax adapter.

## 2.3.1.1 Specifications

- Frequency Range: 8.2-12.4 GHz

- Square Non-Choke Flange

- WR-90

- N-Female Adapter

- Construction: Brass Alloy

- Price: \$129.95

Figure 5: Flann 16094-NF Adapter

## 2.3.1.2 Benefits

- Coaxial adapter port easily accessible

- Usually ships within 24-72 hours

## 2.3.1.3 Drawbacks

- Expensive

- 2.3.2 Omega Laboratories Model 108 WR90 to N-Female Waveguide Adapter Figure 6 is a picture of one option for a waveguide-to-coax adapter.

## 2.3.2.1 Specifications

- Frequency Range: 8-12.4 GHz

- WR-90

- N-Female Connector

- Square Non-Choke Flange

- Construction: Brass Alloy

- Price: \$129.95

Figure 6: Omega Lab. Adapter

## 2.3.2.2 Benefits

- Coaxial adapter port easily accessible

- Usually ships within 24-72 hours

#### 2.3.2.3 Drawbacks

• Expensive

# 2.3.3 WR90 Waveguide Isolator X-Band 8.2 to 12.4 GHz

The Waveguide Isolator Adapter is the preferred option based on its low price and combine capabilities as an isolator. Having the isolator built into the adapter will simplify the radar system, but also creates some complexity with understanding pulse receiving. Figure 7 is a picture of the preferred waveguide-to-coax adapter.

## 2.3.3.1 Specifications

- Frequency Range: 8.2-12.4 GHz

- Price: \$79.95

Figure 7: Waveguide plus Isolator Adapter

# 2.3.3.2 Benefits

- Inexpensive

- Includes an isolator to prevent excessive leakage.

- Leakage would increase the noise figure levels of the system.

- Usually ships within 24-72 hours

## 2.3.3.3 Drawbacks

• Isolator is a non-reciprocal one way device where input to one of the ports goes to a load and is isolated from other port

# 2.4 FPGA

A Field Programmable Gate-Array (FPGA) is needed to control the tasks in the system electronically. The FPGA should have an appropriate clock speed of at least 100 MHz, a VGA port, a Pmod interface, and a USB port. The FPGA should have a clock speed of at least 100 MHz because the higher the clock speed the better the quality. The switching edge needs to be 10ns per sponsor recommendation. The clock speed needs to be 100 MHz to guarantee the 10ns switching capability. Alternating the switches on and off does not occur instantaneously which creates a rise time and settling time. Additional time is needed for settling stability. The VGA port would be solely for the displaying images. The Digilent Pmod interface is used to connect low frequency, low I/O pin count peripheral modules to the host controller boards. This includes the Digital-To-Analog (D/A) and Analog-To-Digital (A/D) converters that are only compatible with Digilent's FPGAs and microcontrollers. The USB port would be useful because it allows the FPGA control to get plugged into a PC. The PC is used to compile the FPGA code that controls the system.

# 2.4.1 Digilent Nexys 2

The Digilent Nexys 2 is the sample our sponsor gave us in terms of what to look for in an FPGA. It was first developed in 2007 and can be seen in Figure 8 [2].

Figure 8: Digilent Nexys 2

# 2.4.1.1 Specifications

- 500K-gate Xilinx Spartan 3E FPGA [2]

- USB-powered

- 8 LEDs, 4-digit 7-seg display, 4 buttons, 8 slide switches

- 50MHz oscillator plus socket for second oscillator

- VGA, PS/2, and serial ports

- Four 12-pin Pmod connectors

## 2.4.1.2 Benefits

The Digilent Nexys 2 is a low cost FPGA, with a price range from \$140 for the academic discount to \$180 for the regular price. The sponsor is also very familiar with this FPGA, saying it is a reliable device thus recommending it.

#### 2.4.1.3 Drawbacks

The 50 Mhz clock speed is not enough for what is desired in this project. This could possibly be supplemented by using a clock multiplier to increase the clock speed if nothing else could be found, but this is undesirable. The Digilent Nexys 2 is also an old model. Since no new devices are made, only left over stock is available for sale.

# 2.4.2 Digilent Nexys 3

The Digilent Nexys 3, shown in Figure 9, is a newer version of the sample FPGA that our sponsor gave us. It is very similar to the Digilent Nexys 2 in terms of characteristics, with minute upgrades and differences [3].

Figure 9: Digilent Nexys 3

# 2.4.2.1 Specifications

- 8-bit VGA port [3]

- 100MHz CMOS fixed frequency oscillator

- On-board USB2 port for programming & data transfer

- GPIO includes 8 LEDs, 5 buttons, 8 slide switches and 4-digit seven-segment display

- 16Mbyte Cellular RAM (x16)

- 8-pin Pmod connectors for lower speed and lower pin-count I/O.

#### 2.4.2.2 Benefits

Very similar to its earlier model the Digilent Nexys 2. This means it has good reviews and our sponsor is somewhat familiar with the brand/model. Has the necessary clock speed of 100 MHz that is desirable for this project.

#### 2.4.2.3 Drawbacks

Price range is from \$139 for the academic discount to \$279 for the regular price. The clock is also fixed at 100MHz, which can be a problem if the clock speed needs to be easily adjusted.

## 2.4.3 Digilent Nexys 4 Artix-7

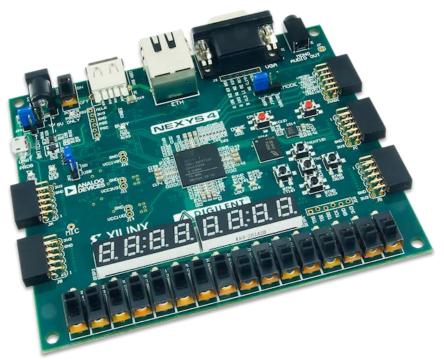

The Digilent Nexys 4 Artix-7, shown in Figure 10, is the newest version of the sample FPGA that the sponsor gave the team. It is very similar to the Digilent Nexys 3 in terms of characteristics, with noticeable upgrades and minute differences [4].

Figure 10: Sigilent Nexys 4 Artix-7

# 2.4.3.1 Specifications

- Internal clock speeds exceeding 450MHz [4]

- On-chip analog-to-digital converter (XADC) 12-bit VGA output

- 16 user LEDs

- Four Pmod ports

- USB HID Host for mice, keyboards and memory sticks

- Two 4-digit 7-segment displays

#### 2.4.3.2 Benefits

Very similar to the Digilent Nexys 3. This means it has good reviews and our sponsor will be familiar with the brand/model. Has the necessary clock speed of 100Mhz, and has the capability of having internal clock speeds of exceeding 450 MHz. The greater the maximum clock speed the FPGA has the better since the signal will come out cleaner.

#### 2.4.3.3 Drawbacks

The price of the Nexys 4 Artix-7 is the highest among the Nexys line of FPGA's. The price range is \$159 for the academic discount and \$320 for the regular price.

# 2.5 D/A and A/D Pmod Converters

The Digilent brand of FPGA's and microcontrollers has a unique Pmod interface which allows for simplification of peripherals. This allows for hardware interface of certain devices (such as A/D and D/A converters) to be pre-designed and the modules can be easily assembled without trouble (no soldering or physical modification of board required). Since the device being used is an FPGA, software configuration is still a must for the components to work, even though the physical layout can just be plugged in.

#### 2.5.1 Digilent PmodDA1 8 bit

Figure 11 depicts an image of the D/A converter module that converts signals from digital to analog at up to one MSa per second. The DA1 uses a 6-pin header connector and as less than one square inch is small enough to be located where the reconstructed signal is needed. [5]

Figure 11: Diglent PmodDA1 8 bit.

#### 2.5.1.1 Specifications

- Four D/A conversion channels

- 6-pin header and 6-pin connector

- Very low power consumption

- Equipped with two AD7303 digital to analog converters

## 2.5.1.2 Benefits

Allows for onboard connecting of a D/A converter by plugging the PMODA1 into the onboard Pmod connector slot. The Pmod connector slot is located on the Nexys 2, Nexys 3, and Nexys 4 models of Digilent FPGA's.

#### 2.5.1.3 Drawbacks

Very limited Selection of D/A converters to be Pmod compatible. This was the only 8 bit A/D Pmod connector that digilent has for sale.

# 2.5.2 Digilent PmodAD1 Two 12-bit

Figure 12 depicts an image of the A/D converter module that converts signals from analog to digital at up to one MSa per second. The DA1 uses a 6-pin header connector and as less than one square inch is small enough to be located at the signal source. [6]

Figure 12: Digilent PmodAD1 Two 12-bit.

# 2.5.2.1 Specifications

- 6-pin header connector

- 6-pin connector

- Very low power consumption

#### 2.5.2.2 Benefits

Allows for onboard connecting of a A/D converter by plugging the PmodAD1 into Pmod connector. The Pmod connector slot is located on the Nexys 2, Nexys 3, and Nexys 4 models of Digilent FPGA's.

#### 2.5.2.3 Drawbacks

Very limited selection of A/D converters to be Pmod compatible. This was the only 12 bit A/D Pmod connector that digilent has for sale.

# 2.6 Voltage Controlled Oscillator (VCO)

An oscillator is an electronic circuit that generates a periodic signal. The signal can be in the form of either a square pulse or a sinusoidal. A voltage controlled oscillator is type of oscillator that uses an applied voltage to control the frequency of the periodic signal that is generated. In this electrical system for this design the VCO generates a high frequency pulse wave of the X-band that powers the system.

# 2.6.1 Hittite Microwave Corporation HMC-C028

The HMC-C028, as shown in Figure 13, is a wideband voltage controlled oscillator that meets the minimum specifications of the design. It was considered because of its operating frequency range, power output, and connector style. [7]

## 2.6.1.1 Specifications

- Operating frequency range: 5-10 GHz

- Provided generation ratio: 0.2 MHz/V

- Output power: +20 dBm

- Phase noise: -95 dBc/Hz

- Single Positive Voltage Supply +8V to +15V

- Operating Temperature: -40°C to 85°C

# C +VDC HMC-C029 VTUNE

Figure 13: HMC-C029

#### 2.6.1.2 Benefits

The HMC-C028 is a chassis mount module; it can be easily mounted to a structure. This is the preferable packaging type for the design. In addition it comes with replaceable SMA connectors allowing ease changeability if they are damaged.

## 2.6.1.3 Drawbacks

The HMC-C028 has a typical return loss of 15 dB. This will contribute to the overall loss in the transmission path and will have to be accounted. It requires a voltage supply of at least 8V @ 185 mA. This voltage is a high relative to the reference voltage of the FPGA.

#### 2.6.2 RFMD VCO-520S/STC

The VCO-520S/STC, depicted in Figure 14, is a hybrid assembled voltage controlled oscillator. It was considered because its operating frequency meets the minimum specifications of the design. The VCO-520S/STC is also a chassis mount module. [8]

#### 2.6.2.1 Specifications

- 4900MHz to 5900MHz VCO

- 5V Operation

- -1dBm Typical Output Power

- -77dBc/Hz at 10kHz

- -102dBc/Hz at 100kHz

- -122dBc/Hz at 1000kHz

Figure 14:RFMD VCO-520S/STC

## 2.6.2.2 Benefits

The VCO-520S/STC is a chassis mount module which is the preferred package type. It has relatively low supply voltage in comparison to the output of the FPGA. Also the output impedance of this module is 50  $\Omega$ ; this important because most devices have an input of impedance of 50  $\Omega$ , thus impedance matching between this and a receiver is not a concern.

# 2.6.2.3 Drawbacks

The VCO-520S/STC has a low output power. The maximum value is 2 dBm. If this VCO was the driver to a device that need a higher amount of input power, an amplifier would be needed

# 2.7 IQ Demodulator

The theory behind IQ demodulation is to represent the input RF signal as a combination of two double sideband modulated quadrature carrier signals. The IQ demodulator samples the input RF signal twice however at a phase difference of 90°. This allows the relative phase of the components of the signal to be measured. The I output of the IQ demodulator is the real part of the signal while the Q output is the imaginary part of the signal. Together these signals provide the amplitude and phase shift of the input RF signal.

## 2.7.1 Polyphase Microwave Quadrature Demodulator - AD60100B

The AD60100B, shown in Figure 15, is a quadrature demodulator that converts the RF signal that is input to the baseband I and Q outputs whenever a LO signal is applied. The frequency range of the LO/RF signal is 6-10 GHz. [9]

# 2.7.1.1 Specifications

- LO/RF Frequency: 6 10 GHz

- I/Q Bandwidth: 275 MHz

- Input IP3: +22 dBm

33

Figure 15:AD60100B

- Input P1dB: +12 dBm ٠

- Amplitude Imbalance:  $\pm 0.1 \text{ dB}$

- Phase Error: 2 Degrees

- LO Power: +5 dBm

- DC Supplies: +5V @ 110 mA, -5V @ 40 mA

#### 2.7.2 SigaTek I Q Demodulator – QD27A11

The QD27A11, depicted in Figure 16, is an IQ demodulator that converts the RF signal that is input to the baseband I and Q outputs whenever a LO signal is applied. The carrier frequency LO is 4-6 GHz.

#### 2.7.2.1 Specifications

- Carrier frequency range: 4-6 GHz

- RF frequency range: LO±DC-300

- Maximum conversion loss: 9 dB

- Maximum Amplitude balance: 1 dB •

Figure 16: QD27A11

#### 2.7.2.2 Benefits

The QD27A11 module is a chassis mount device and can interface with SMA connector devices. Its operating frequency is within the design specifications therefore the frequency of any input signals do not have to be increased or decreased.

#### 2.7.2.3 Drawbacks

This has a conversion loss of the QD27A11 is 9 dB which is higher than the AD60100B. This will have to be accounted for in the calculations.

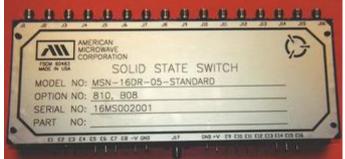

## 2.8 Switches

The switches are very important components in the electrical system. They provide the capability of generating a switched output which gets delivered to multiple components by a single driver. The speed at which the output is switched between the loads is based on the frequency of the control signal.

#### 2.8.1 Single Pole Double Throw (SPDT)

The single pole double throw creates a short circuit between the each of the two RF channels and the common channel. The SPDT switch is needed in this electrical system because it allows the VCO to provide an input to both the transmit path and the IQ Demodulator.

#### 2.8.1.1 Hittite HMC-C058

The Hittite HMC-C058, depicted in Figure 17, is a high isolation non-reflective SPDT switch. It has an operating frequency of DC to 18 GHz. [10]

#### 2.8.1.1.1 Specifications

- Operating Frequency Range: DC 18 GHz

- Operating Temperature Range: -55°C to 5°C

- Maximum Insertion Loss:

- 2.4 dB @ DC-6 GHz

- 2.8 dB @ DC-10 GHz

- 5.5 dB @ DC-18GHz

Figure 17: HMC-C058

#### 2.8.1.1.2 Benefits

The HMC-C058 is a module component with replaceable SMA connectors. It offers high isolation with low insertion loss as well as fast switching speeds (3 ns Fall/Rise times.) The HMC-C058 is non-reflective and has an impedance of  $50\Omega$ .

#### 2.8.1.1.3 Drawbacks