### COSMICi: High Energy Particle Detector

<u>Group 25</u> Aarmondas Walker George Chakhtoura Samad Nurideen Brian Kirkland Juan Calderin Michael Dean

0

<u>Sponsor</u> FAMU

### **Project Goal**

Install and implement a network of Cosmic Ray detectors that will triangulate the origins of the Ultra High Energy Cosmic Ray shower events.

# **Component Overview**

- Scintillators

- FPGA

- Gel Ware

- Network Component Enclosure

- Cooling system

- Structural Supports

### Network System Diagram

## **Concept Generation**

- Network System operational speed

- Use Logic Locking to optimize speed

- Create more efficient program

- Support Structure for Detectors

- I Beam Suspension System

- Wall Mount Brackets

- CLC Placement

## **Concept Generation Cont...**

- Stratix II Cooling System

- Simple fan heat dispersal

- Liquid cooling system

- Peltier method for isolated heat removal

- Network System Enclosure

- Enclosed PC tower

- Transparent enclosure for public aesthetics

- Solid mounting points for all boards and power supply

### **Concept Selection**

| Component                        | Concept Selection                           |

|----------------------------------|---------------------------------------------|

| Network System Operational Speed | Increase current program speed              |

| Detector Support Structure       | I Beam suspension and Wall Mount<br>Support |

| Cooling System                   | Peltier Method                              |

| Network System Enclosure         | Base plate with transparent enclosure       |

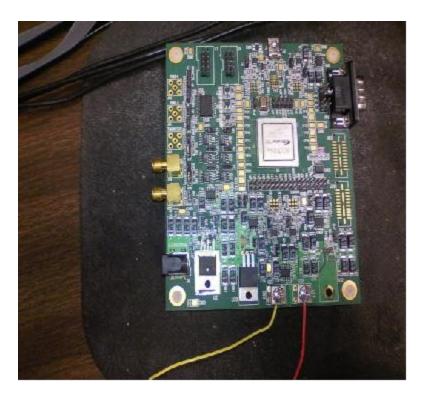

# Front End Digitizer Module

•Main board that retrieves signals from scintillators and sends to server for data processing.

•Houses Stratix II chip

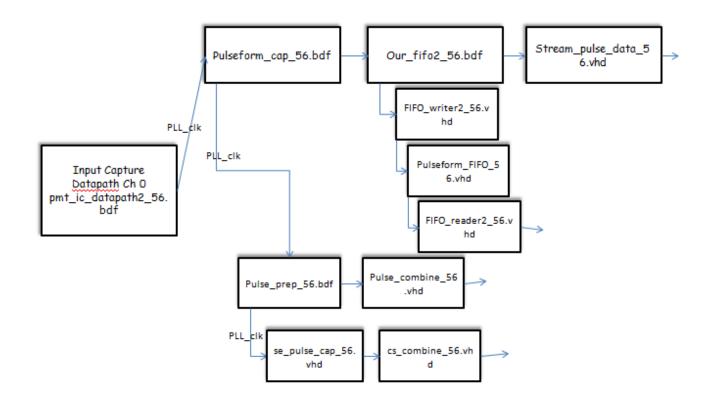

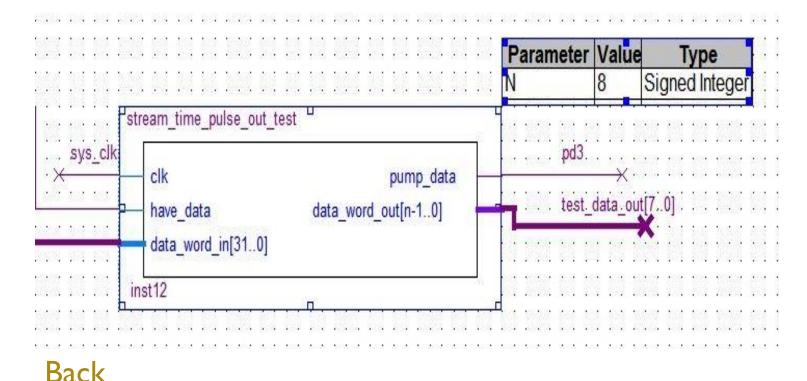

### Input Capture Data Path

#### Input Capture Datapath Ch O "pmt\_ic\_datapath2\_56.bdf"

#### Logic Locking of High Speed Components and Bit Width Reduction

The internal timing counter was 64-bits wide, giving over 10 years data values

This value was reduced to 56-bits and still give 4.5 years

Previous Speed 200 MHz Desired Speed 500 MHz Achieved Speed 323 MHz

To see the system memory improvement specifications after reduction please refer to <u>Appendix A</u>

# Logic Locking Cont...

- Utilized Quartus' Logic Locking to obtain optimal operational running speed of 500 MHz

- All components utilizing the PII\_clock line will be locked

- Logic Locking settings: State - Floating or Locked Size - Auto or Fixed Reserved - On/Off -Enforcement - Hard or Soft Origin - Floorplan Location

Please refer to <u>Appendix A1</u> for Logic Locking methods

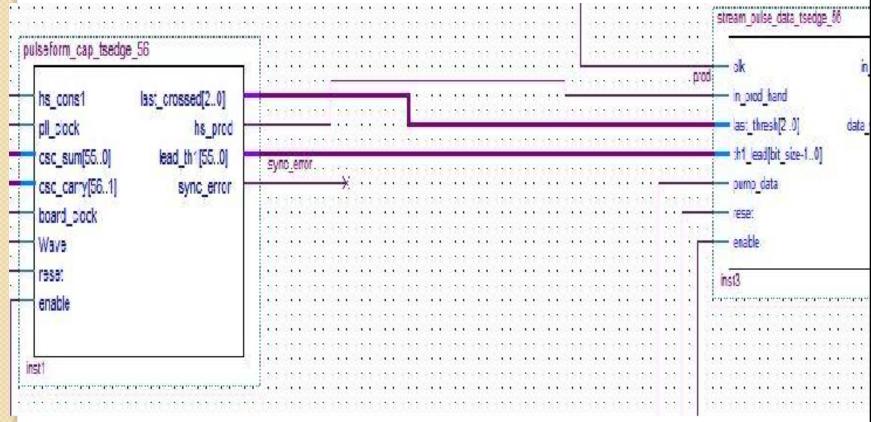

# Timing Sync Data Paths

#### Before Modification

| seform_cap_56  |                  | clk                | out_hs_proc             |

|----------------|------------------|--------------------|-------------------------|

|                |                  | in_hs_prod         | in_hs_cons              |

| hs_cons1       | last_crossed[20] | out_hs_cons        | last_cr[20]             |

| pll_clock      | hs_prod          | last_crossed[20]   | th1_ld[550]             |

| csc_sum[550]   | lead_th1[550]    | <br>lead_th1[550]  | th1_tr[550]             |

| csc_carry[561] | trail_th1[550]   | trail_th1[550]     | th2_ld[550]             |

| board_clock    | lead_th2[550]    | <br>lead_th2[550]  | th2_tr[550]             |

| Wave[16]       | trail_th2[550]   | trail_th2[550]     | th3_ld[550]             |

| reset          | lead_th3[550]    | lead_th3[550]      | th3_tr[550]             |

| enable         | trail_th3[550]   | <br>trail_th3[550] | th4_ld[550]             |

|                | lead_th4[550]    | lead_th4[550]      | th4_tr[550]             |

|                | trail_th4[550]   | trail_th4[550]     | th5_ld[550]             |

|                | lead_th5[550]    | lead_th5[550]      | th5_tr[550]             |

|                | trail_th5[550]   | trail_th5[550]     | th6_id[550]             |

|                | lead_th6[550]    | lead_th6[550]      | th6_tr[550]             |

|                | trail_th6[550]   | trail_th6[550]     | BUF_FULL                |

|                |                  | reset              | and the strength of the |

# Timing Sync Data Paths Cont...

#### After Modification

#### • Testing Shown in <u>Appendix C</u>

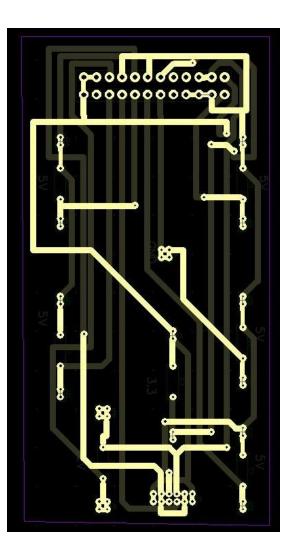

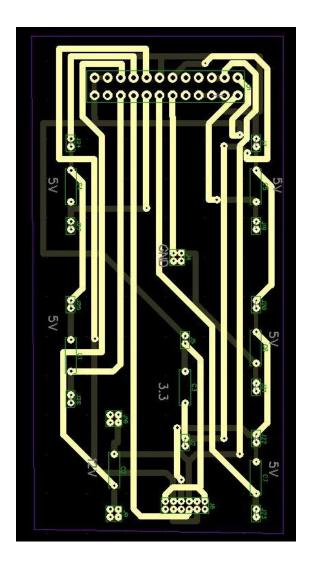

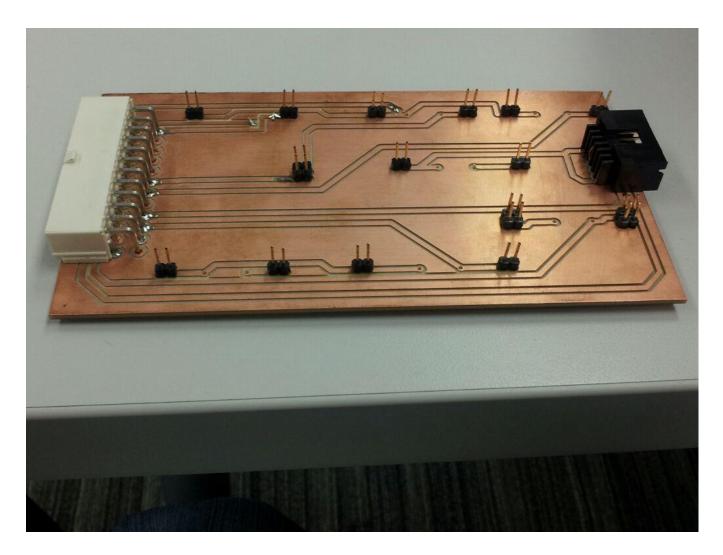

#### **Power Distribution Board**

#### Final Power Board

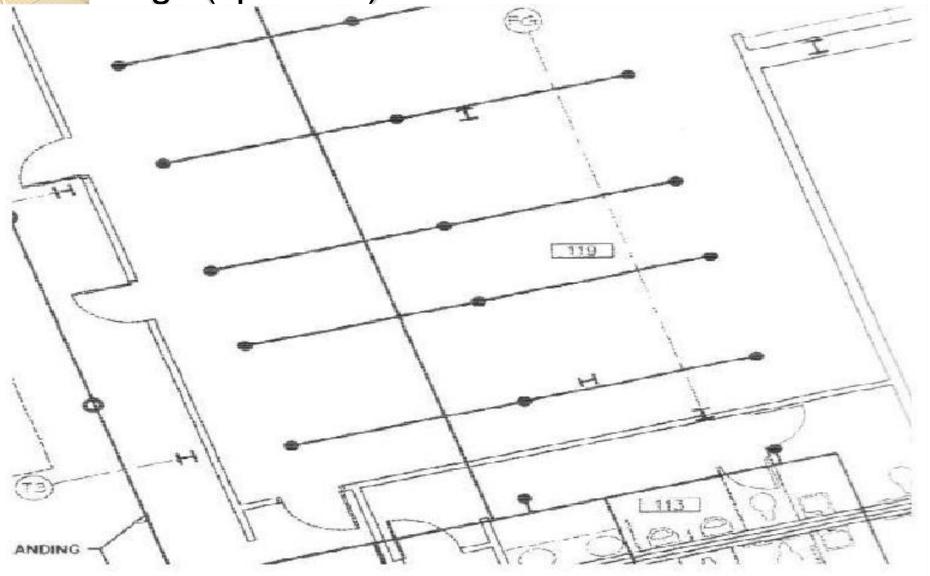

## **Detector Support Structure**

- 3 Scintillators

- Each 30' apart creating equilateral triangle

- Two shelf mounted

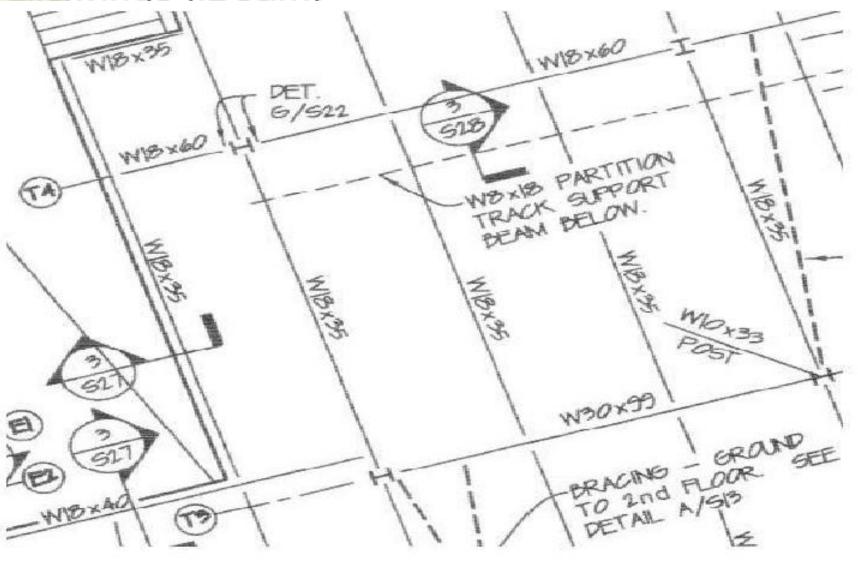

- One suspended from I Beam through dropdown ceiling

- Wired to central network enclosure

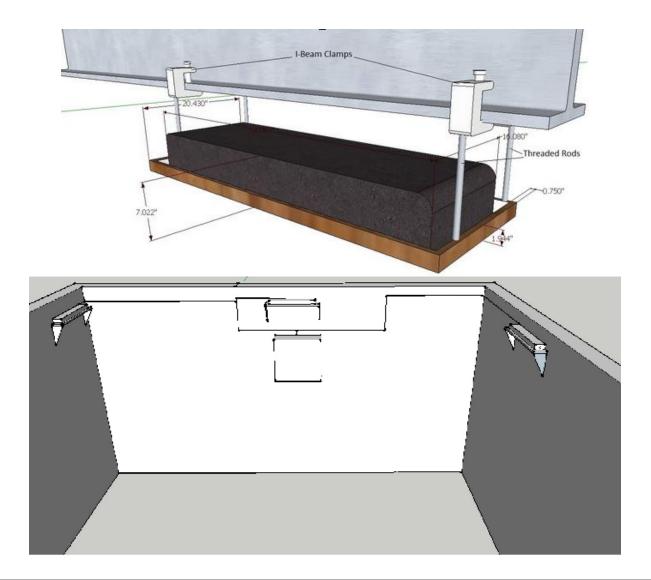

### **Suspension & Shelving Design**

#### Suspension & Shelving Design Cont...

- Components of shelving units:

- Each detector is placed in a foam insulated gun case weighing 25 lbs

- Case is mounted and supported by 3 L brackets into the drywall

- Single bracket weight capacity of 25 lbs

- Components of suspended units:

- 4 I Beam Clamps

- 4 threaded rods connected from clamp to structure

- Structurally supports 100 lbs

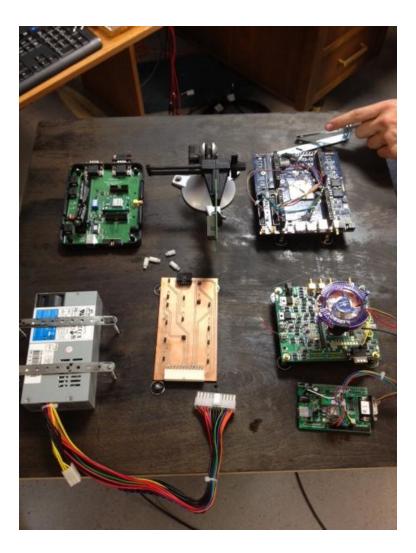

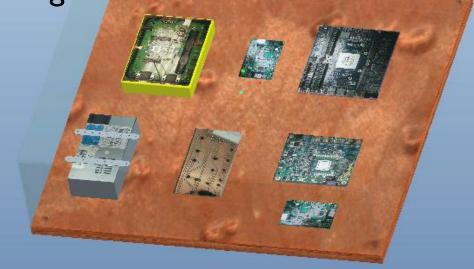

### Network System Enclosure

Enclosure Houses: FEDM Board Power Supply Power Distribution Board Oscillator GPS Board DE3 Board WiFi Board WiFi Board

#### Network System Enclosure Cont...

- All enclosure mounted on birch wood base plate.

- Enclosed in plexi-glass housing

- Latched top for accessibility

- Suspended from I Beam in center of room components facing down

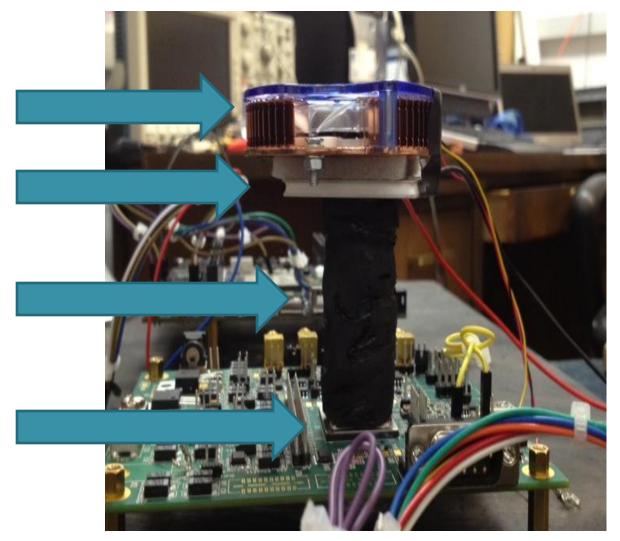

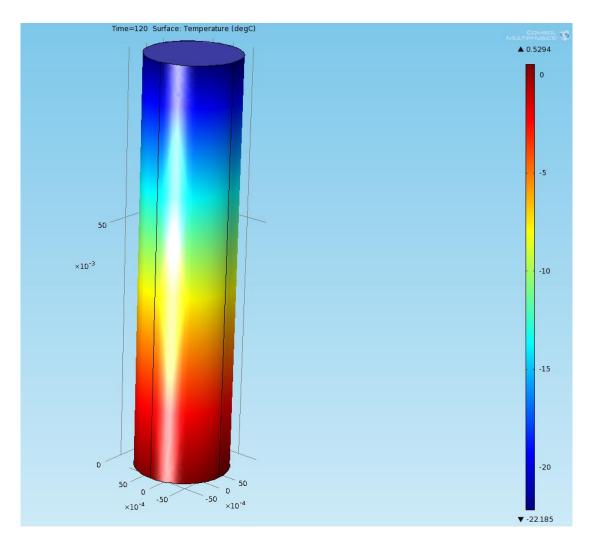

# **Cooling System**

- Used Peltier method for the Stratix II chip provides continued isolated cooling

- Mounted from base plate to fan, held in low compression against chip

- Prevents overheating and system shut down and restart which occurs at 53° C

- Maintains operational temperature at I° C

Appendix B1

# Cooling System Cont...

Copper Fin & Fan Heat Sink

Thermoelectric Cooler

Polyurethane insulated Copper rod

Stratix II chip

# Budget

| D. Expense                           | Quantity | Unit Price \$ | Total \$ |

|--------------------------------------|----------|---------------|----------|

| Equipment                            |          |               |          |

|                                      |          |               |          |

| Structural Support                   | 4        | \$2.39        | \$9.56   |

| Beam Clamp 3/8"<br>Threaded Rod 3/8" | 4        | 8.89          | 35.56    |

| Hex Nut Full 3/8"<br>100PK           | i        | 6.28          | 6.28     |

| Flat Washer 3/8" 100<br>PK           | 1        | 5.09          | 5.09     |

| Cooling System                       |          |               |          |

| Peltier Cooler                       | 2        | 7.50          | 13.00    |

| Heat Pipe                            | 1        | 41.00         | 41.00    |

| Fan                                  | 1        | 21.27         | 21.27    |

| Enclosure                            |          |               |          |

| Acrylic Cover                        | 1        | 68.57         | 68.57    |

| Birch Plywood<br>Baseplate           | 1        | 9.99          | 9.99     |

| Mounting Hardware                    | 1        | 20.00         | 20.00    |

| Power Supply<br>Components           |          |               |          |

| Headers                              | 7;1      | 2.50; 5.00    | 22.50    |

| Power Distribution<br>Boards         |          | 10            | 20       |

| Connectors                           | 3        | n/a           | 15.00    |

| Battery                              | 2        | 65            | 130      |

| Total Equipment Cost                 |          |               | 210.32   |

| Total Project Cost                   | -        |               | \$439.09 |

# **Circuit Speed Testing**

- The Classic Timing Analyzer Tool was used to test circuit speed

- Feature gives estimate running speed from current compiled data with current FEDM design

| Classic Timing Analyzer Tool            |                                                 |

|-----------------------------------------|-------------------------------------------------|

| Registered Performance tpd tsu tco th C | Custom Delays                                   |

| Clock:                                  |                                                 |

| Value                                   |                                                 |

| From<br>To                              |                                                 |

| Clock period                            |                                                 |

| Frequency                               |                                                 |

|                                         | 100 125 150<br>75 175<br>50 200<br>25 0 MHz 250 |

# Structural Support Testing

- Shelving Units tested in dry wall using 50lb weights

- No failure

- No bracket dislodgment from wall

- Successful support testing

# **Enclosure Testing**

- Supporting 2 lbs of hardware inverted

- Using deflection test

- 80lb weight caused <4mm deflection</li>

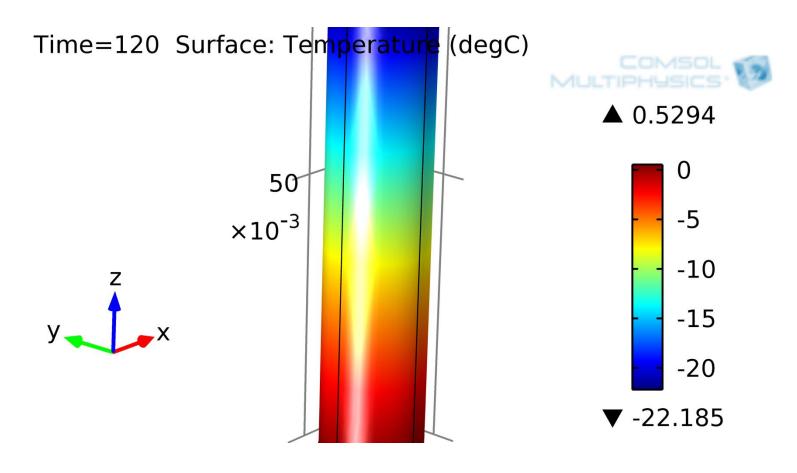

# **Cooling System Testing**

- COMSOL rendering to support calculations.

- Successful system test of 2°C at operational speed of 353 MHz

- Slight condensation build up at thermo cooler contact point

- Solution: Seal point of contact with small polyurethane ring

Sample Calculations <u>Appendix B</u> COMSOL Rendering <u>Appendix B2</u>

# **Complete System**

- Complete system test at 353 MHz

Have not reached 500 MHz yet

- Total system test proved successful

- Stratix chip cooled to 2°C

- Obtained small amount of data

- No high cosmic activity at the time of testing

### Questions?

# Appendix A

Before:

Slow Corner Fmax for high-speed counter: 211.28MHz Logic Utilization: 24,314 / 27,104 (90%) = 2,790 remaining Dedicated logic registers used: 21,878 / 27,104 (81%) = 5,226 remaining M512 blocks: 193/202 (96%) = 9 remaining M4K blocks: 144/144 (100%) = 0 remaining M-RAM blocks: 1/1 (100%) = 0 remaining

• After:

Slow Corner Fmax for high-speed counter: 213.13 MHz (slightly better) Logic Utilization: 22,007 / 27,104 (81%) = 5,097 remaining (almost 2x better)

Dedicated logic registers used: 19,463 / 27,104 (67%) = 7,641 remaining M512 blocks: 188/202 (93%) = 24 remaining (more than 2x better)

M4K blocks: 144/144 (100%) = 0 remaining (same)

M-RAM blocks: 1/1 (100%) = 0 remaining (same)

#### <u>Back</u>

# Appendix A I

State - Floating or Locked

Floating regions allow Quartus to determine the appropriate location of the block, while Locked uses a user defined location

Size - Auto or Fixed

Auto lets Quartus handle sizing while Fixed uses user defined sizing and shaping

Reserved - On/Ŏff -

Enabling allows Quartus to utilize resources from this region for entities not assigned to this region

Enforcement - Hard or Soft -

Soft enforcement allows deference of the region to timing constraints, allowing entities to leave region if performance is improved. Hard enforcement does not abide by the relocation of entities

Origin - Location on Floorplan -

Defines the locations of the logic lock region

**Back**

# Appendix B

- Q=k\*a\*(Thot-Tcold)/d

- Established Heat Rate (from current system) Q= 126.563 W

- Cross Sectional Area a= 5cm<sup>2</sup>

- Desired Rod Length d= 8.4cm

- Thermal Conductivity of Copper k= 401 W/m\*K

- Running Temperature (Thot) Thot= 53°C (326K)

- Desired Running Temp(Tcold) Tcold= 0°C (273K)

**Back**

# Appendix BI

- Updated Specs With New Thermoelectric Cooler

- Q=40W

- =>Desired Rod Length d=3.3in

- COP= $T_C/(T_H-T_C)$

- EFF=  $(T_H T_C)/T_C$

- Eff=9.05%

- COP=11.05

# Appendix B2

## Appendix B3

### Appendix C

#### Timing Sync Module Used for Testing

#### **Material Selection**

#### Need To use plots from Ashby's textbook to find the best material

**Material Index**

Shows which guide lines to use

Gives an idea of which plots to use

#### Must use Modulus vs. Relative cost plot

**Relative cost**

Necessary to correct values and remove influence of inflation and units of currency

$C_{v,r} = \frac{\frac{Cost_{material \, selection}}{kg} * Density \, of \, material \, selection}{\frac{Cost_{steel}}{kg}} * Density \, of \, mild \, steel \, rod$

#### Material Choice: References

- Aluminum Plate. Digital image. Made-in-china.com. Web. 29 Nov. 2011. <http://image.made-in- china.com/2f0j00bBpEIOzJZvuV/Fireproof-Aluminum-Plate.jpg>.

- Ashby, M. F. *Materials Selection in Mechanical Design*. Burlington, MA: Butterworth- Heinemann, 2011. Print.

- Baltic Birch Plywood. Digital image. Web. 29 Nov. 2011. <http://images.rockler.com/rockler/images/63388-01- 200.jpg>.

- "MDF Board FAQ Tutorial." *DIY Audio* & Video FAQs, Tutorials, and Calculators for Speaker Boxes, Crossovers, Filters, Wiring and More. Web. 29 Nov. 2011. <a href="http://www.diyaudioandvideo.com/FAQ/MDF/>">http://www.diyaudioandvideo.com/FAQ/MDF/></a>.

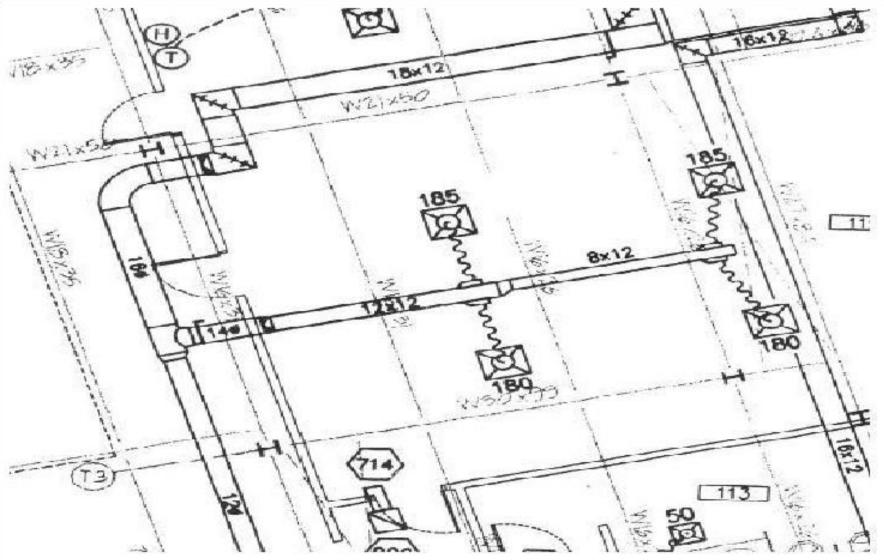

Drawings (vent)

#### Drawings (sprinkler)

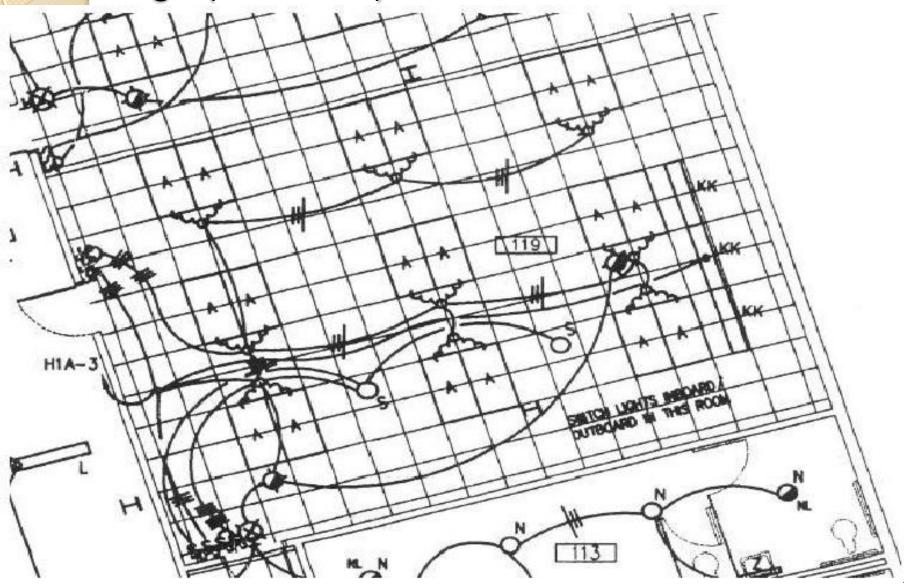

#### Drawings (iBeam)

#### Drawings (electrical)