# Digital Beamsteering Phased Array

Team 311 Sponsor: L3Harris April 7th, 2022

#### **Team Introductions**

Katheryn Potemken Antenna Lead

Tiernen Pan Team Lead / Software Engineer

Christian Balos Software Engineer

William Snyder Hardware Engineer

Andrew Cayson Hardware Lead

# Sponsor, Advisors, and Assisting Instructor

Assisting Instructor: Dr. Arigong

Advisor:

Dr. Uwe Meyer-Baese

Customer: Dr. Hooker

Sponsor: L3Harris

#### **Outline**

- Project Background

- Design Components

- Software Design

- PCB Design

- System Design

- System Results

- Intermediate Testing

- Hardware Assembly

- Final Testing

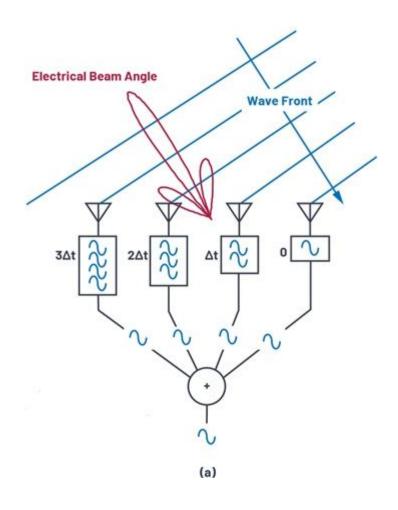

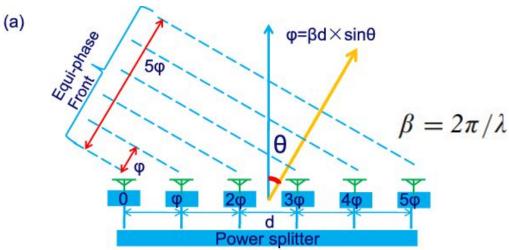

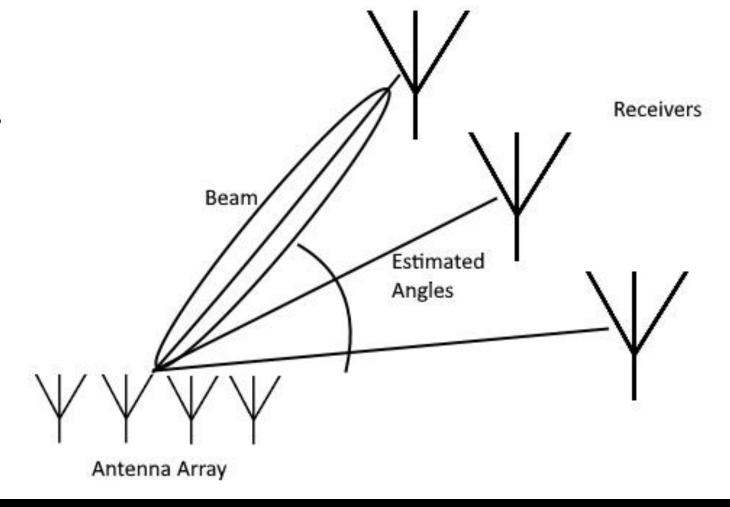

#### What is Beam Steering?

- What is Beam Steering?

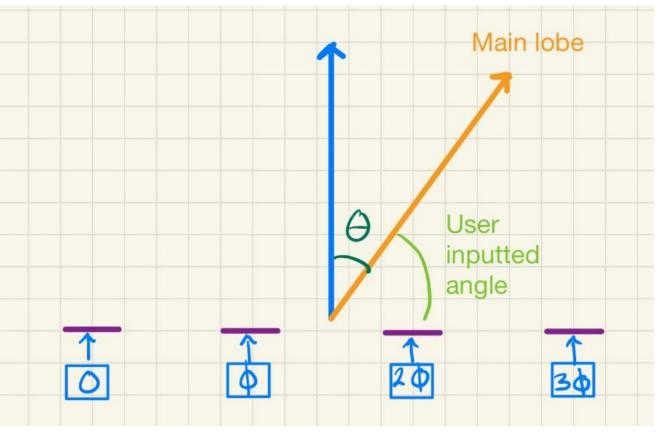

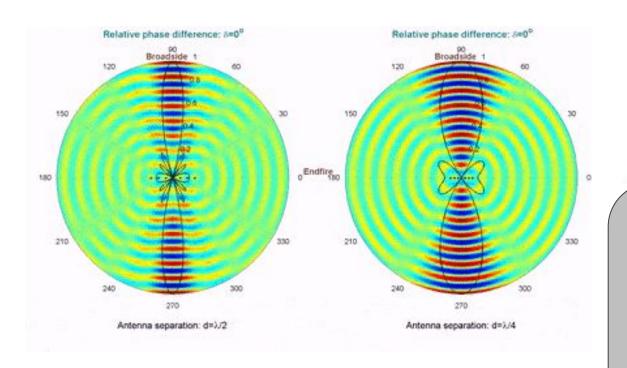

- Beam Steering is the usage of phase shifting within an antenna array to control the direction of the main lobe

- This main lobe consists of each antenna's output constructively interfering with one another

- Why do we need Beam Steering?

- The motivation for beam steering is the need for higher data transmission rates

- Higher quality signal to receivers, with less errors

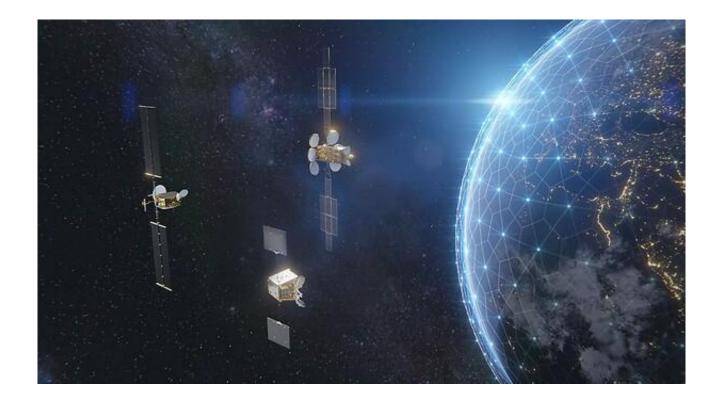

#### Market

- Civilian

- 5G communications

- Satellite to Ground

Communications

- Military

- Improving speed and range of Radar Systems

#### **Project Specifications**

- Operate at 2.4 GHz, which is within the ISM band

- Project parts include:

- Upconverters

- 4 Antennas

- FPGA

- Direct Digital Synthesis (DDS)

- o PCB

- Voltage Controlled Oscillators

- Amplifiers

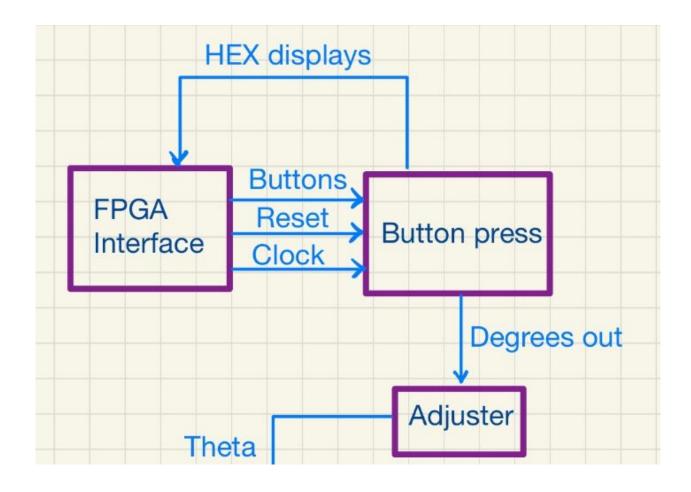

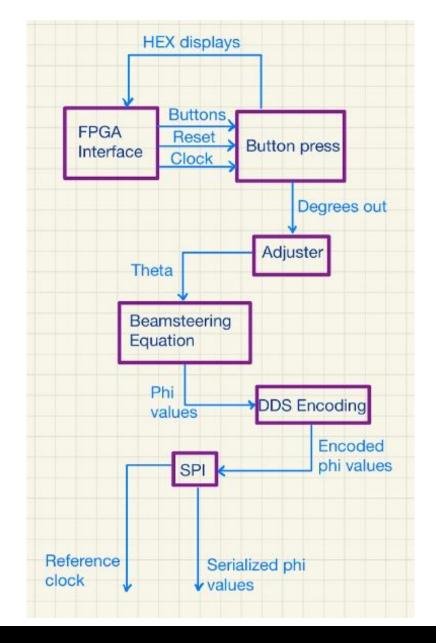

#### **FPGA** Interface

- Push Buttons and 1 switch

- HEX display

#### **Button Press Component**

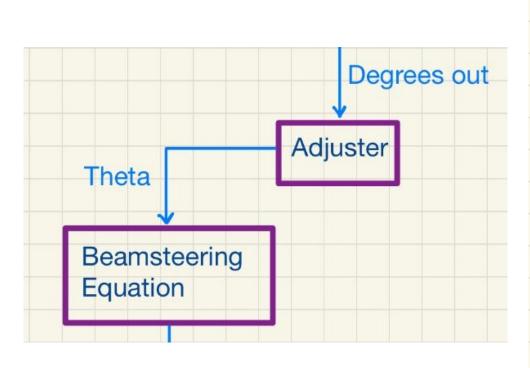

#### **Adjuster Component**

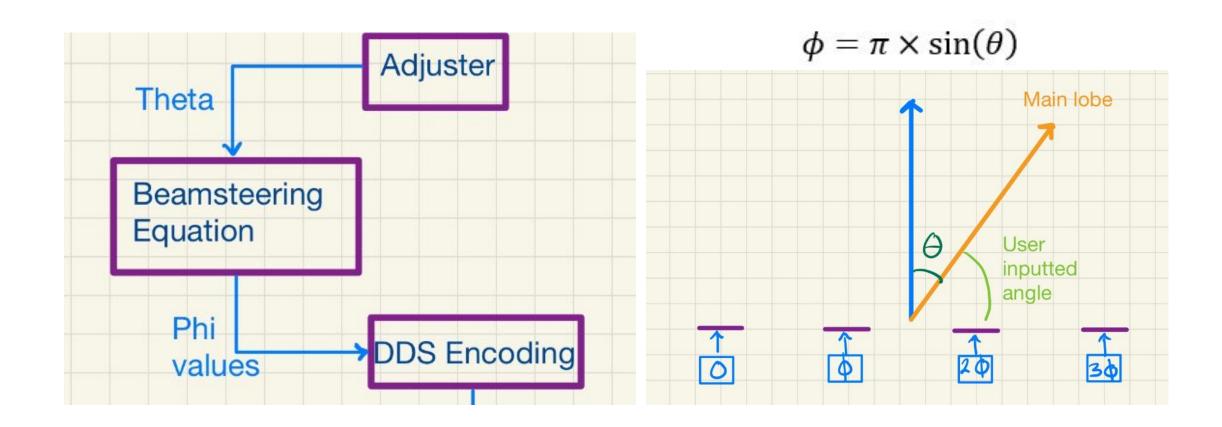

Implementing the Beamsteering

**Equation**

$$d = \frac{\lambda}{2} \qquad \qquad \phi = \frac{2\pi}{\lambda} d \times \sin(\theta)$$

$$\phi = \frac{2\pi \lambda}{\lambda} \times \sin(\theta) \to \phi = \pi \times \sin(\theta)$$

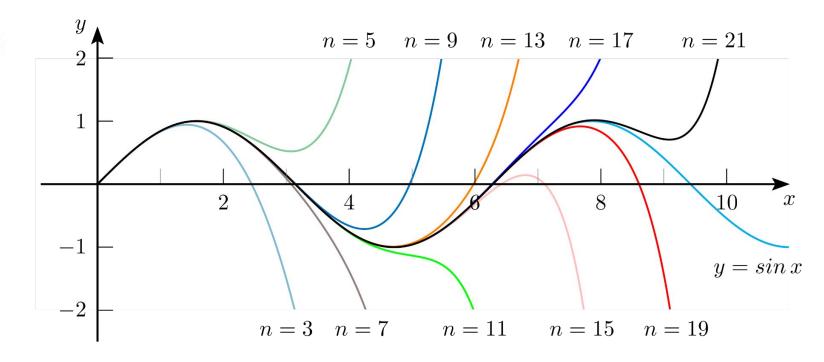

# Taylor Series to Implement the Sine Function

$$\sin(x) = x - \frac{x^3}{3!} + \frac{x^5}{5!} - \frac{x^7}{7!} + \cdots$$

$$=\sum_{n=0}^{\infty}\frac{(-1)^n}{(2n+1)!}x^{2n+1}$$

### **Beamsteering Equation Component**

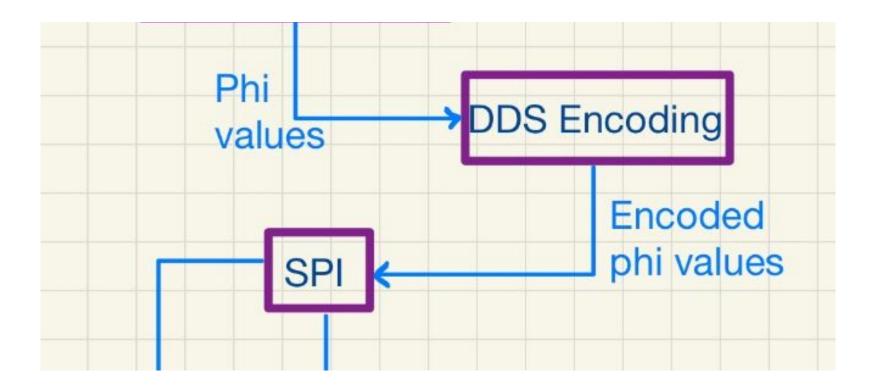

#### **DDS Encoder Block**

• Has a resolution of 0.02197 *degrees*

$$\circ$$

0 = 0, 1 = 0.02197, 10 = 2 x 0.02197, 11 = 3 x 0.02197

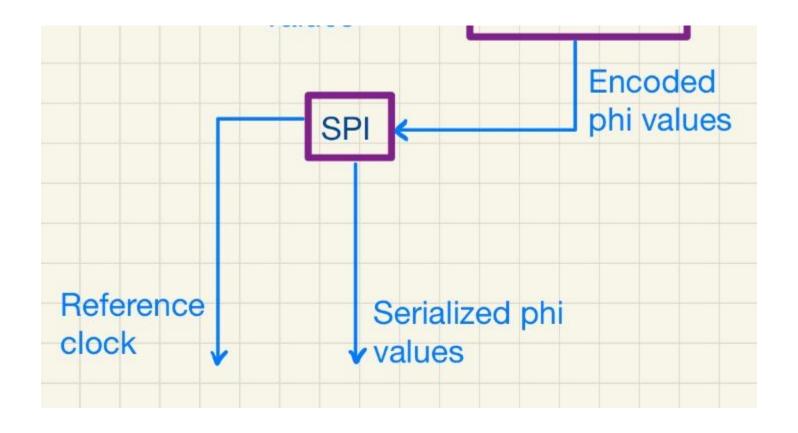

#### SPI block

### **Full Block Diagram**

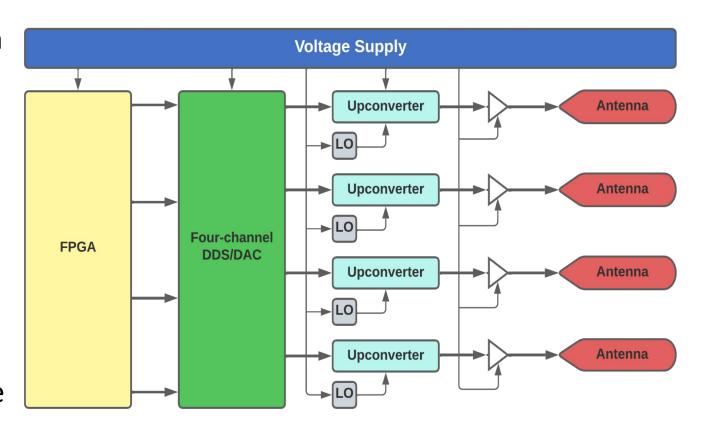

#### **System Design**

- Buttons on the Cyclone V serve as inputs for the array's desired beam angle

- The FPGA communicates with the DDS via SPI

- The DDS converts the signal from Digital to Analog and adjusts the phase as necessary.

- Finally, the analog signal will be upconverted to 2.4 GHz and will be transmitted via antenna.

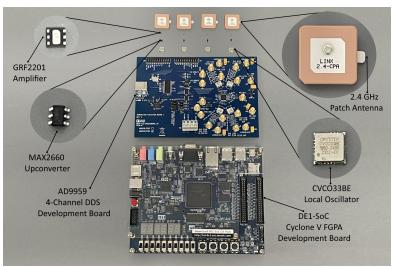

#### **Components Design**

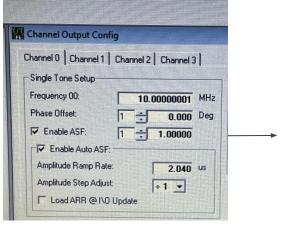

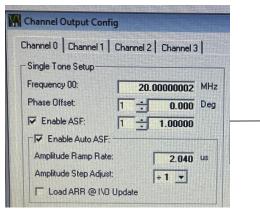

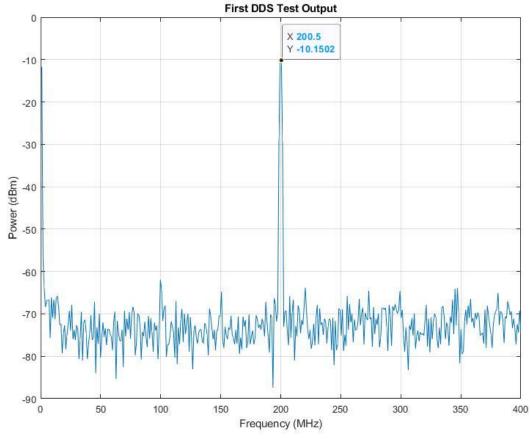

- AD9959 generates a 200.5 MHz signal and adjusts the phase difference on each of the four channels.

- Each channel contains an oscillator, upconverter, and amplifier.

- Amplifier output is connected to 2.4 GHz patch antenna.

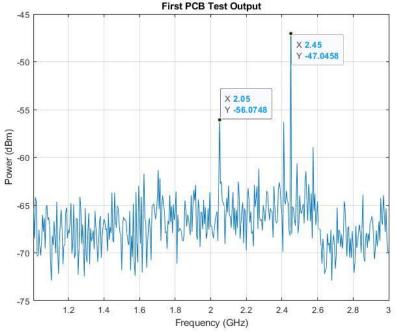

- Oscillator generates a 2.2 GHz signal and mixes with the 200.5 MHz signal to create the 2.4 GHz signal.

$$\cos(2.2 \times 10^9) \cdot \cos(200.5 \times 10^6) = \frac{1}{2} (\cos(2.45 \times 10^9) + \cos(2.05 \times 10^9))$$

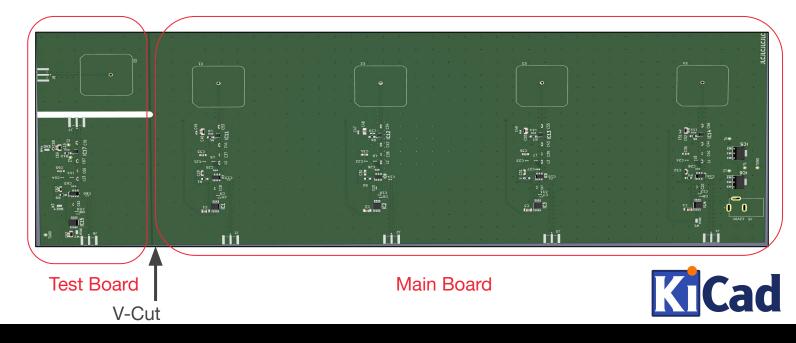

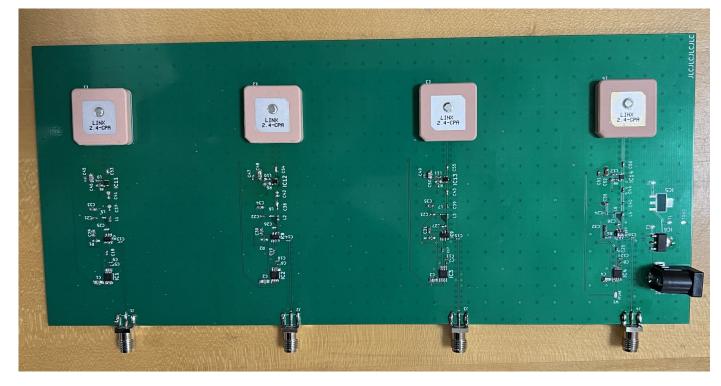

#### **PCB Design**

- RF Traces are **0.562mm** thick for  $50\Omega$  line impedance

- Antennas placed  $\lambda/2 = 62.5$ mm apart

- Vias in grid placed  $\lambda/20 = 6.25$ mm apart

- Vias along traces placed  $\lambda/60 = 2.08$ mm apart

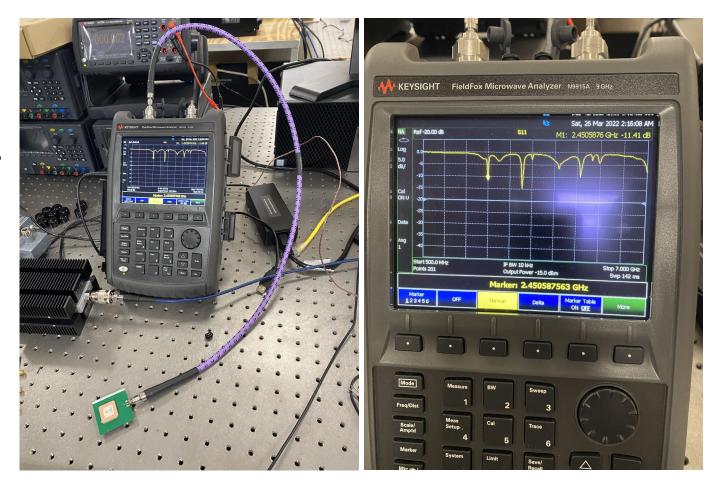

#### **Intermediate Testing - Antenna**

- Soldered two antennas to PCB cutouts

- Two different solder jobs

- Better quality solder job leads to greater antenna efficiency

- At 2.4 GHz, return loss is

-11.41 dB

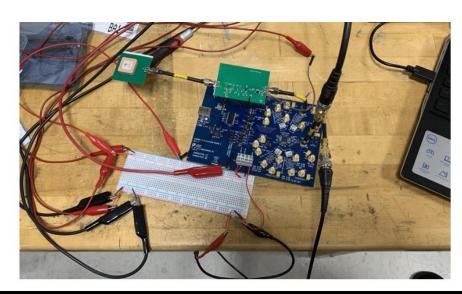

### **Intermediate Testing - Components**

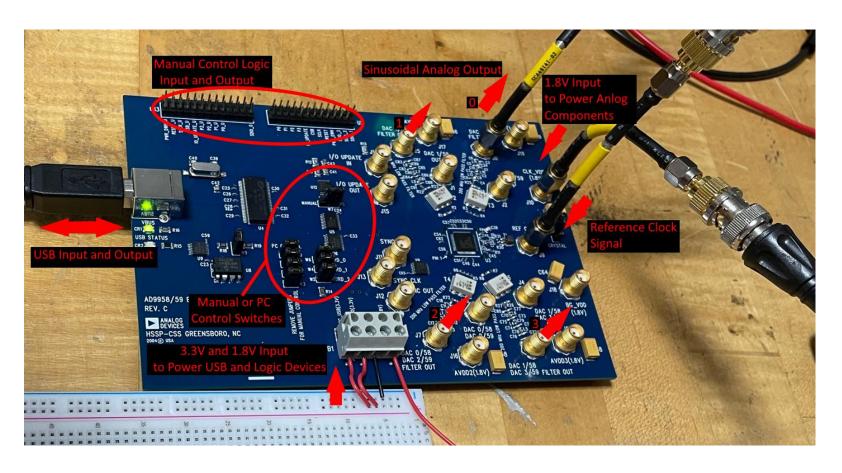

- Connected it to the DDS and powered the system through a breadboard

- Measured output power through microwave analyzer

- Two signals appeared

- At 2.45 GHz, out power is -47dBm

- SPECs are met for frequency but not power

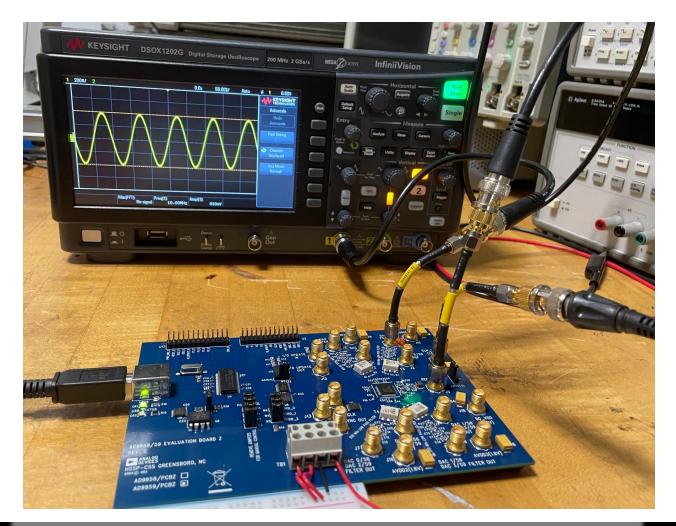

#### **AD9959 Direct Digital Synthesis**

- Changes For Final Design

- Power supply

- No USB

- Manual Mode

- FPGA Wired to LogicInput and Output

- Crystal Oscillator

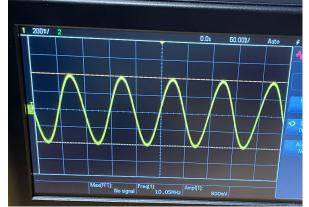

#### **DDS Test Results**

**Evaluation Software**

#### **Frequency Analysis**

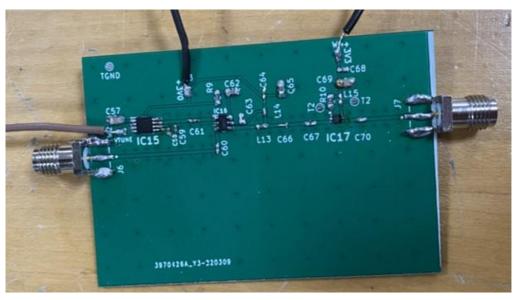

#### **Hardware Assembly**

Main PCB: Antenna Array

#### Test PCB:

Microscope View:

**ELECTRICAL ENGINEERING**

#### **Final Testing**

- Final testing

- o Dr. Arigong's Lab

- Series of receivers

#### **Presentation Recap**

- Project Background

- Design Components

- Software Design

- PCB Design

- System Design

- System Results

- Intermediate Testing

- Hardware Assembly

- Final Testing

#### References

#### Datasheets:

- https://www.mouser.com/datasheet/2/256/MAX2750-MAX2752-15124

50.pdf

- https://www.mouser.com/datasheet/2/256/MAX2660-MAX2673-15153 97.pdf

- https://www.mouser.com/datasheet/2/777/GRRF S A0010122589 1-2 575831.pdf

- https://www.mouser.com/datasheet/2/238/LNNC S A0009494921 1-2 551007.pdf

#### **Questions?**